# Comparative Analysis of High Power Density Bidirectional DC-DC Converters for Portable Energy Storage Applications

Kostiantyn Tytelmaier<sup>1</sup>, Janis Zakis<sup>2</sup>, Oleksandr Husev<sup>1,3</sup>, Oleksandr Veligorskyi<sup>1</sup>,

Maksym Khomenko<sup>1</sup>, Dmitri Vinnikov<sup>3</sup>

<sup>1</sup>Department of Biomedical Radioelectronics Apparatus and Systems,

Chernihiv National University of Technology,

Shevchenko St. 95, 14027 Chernihiv, Ukraine

<sup>2</sup>Institute of Industrial Electronics and Electrical Engineering, Riga Technical University,

Azenes St. 12/1, LV-1048, Riga, Latvia

<sup>3</sup>Department of Electrical Engineering, Tallinn University of Technology,

Ehitajate St. 5, 19086 Tallinn, Estonia

kostya.tytelmaier@inel.stu.cn.ua

Abstract—Bidirectional DC-DC converters are an essential part of modern power systems, such as electric vehicles and renewable energy. The paper presents a comparative analysis of bidirectional DC-DC converters suitable for high power density application without galvanic isolation. It is based on the comprehensive comparative analysis of conduction losses, voltage stress on semiconductors and passive component size. Continuous conduction mode of three widely used bidirectional topologies (cascaded, two-phase interleaved with and without charge-pump) are analysed. Selected analytically calculated evaluation criteria are compared for a wide range of the output voltage level. The best solution is selected for experimental realization based on GaN transistors.

Index Terms—Bidirectional power flow; Circuit analysis; DC-DC power converters; Pulse width modulation converters.

#### I. INTRODUCTION

Recent years have seen a drastic increase in the use of Renewable Energy Sources (RESs) and all types of Electric Vehicles (EVs). A power capacity recorded last year was: solar PV capacity increased by 22 %, constituting 227 GW; wind power capacity increased by 14.5 %, amounting to 433 GW [1]. Also, as compared to 2014, in 2015, electric car stock almost doubled, reaching 1.26 million [2]–[4]. Alternative power sources (compact wind turbines or thin-film solar panels) have become a development trend for portable applications [5]–[11]. Flexible PV blanket mounted on any surface [12], [13] will be quite useful in many applications for charging portable electronic devices.

In general, the technologies described require bidirectional power interface with minimum losses between two DC-busses or a DC-bus and an energy storage device (battery, supercapacitor, etc.). For these purposes, Bidirectional DC-DC Converters (BDCs) should be used. In

Manuscript received 21 May, 2018; accepted 2 October, 2018.

This research is supported by grants (No. 0116U004695 and No. 0116U006960) from the Ukrainian Ministry of Education and Science and has been co-supported by Latvian National Research Program "LATENERGI" and Latvian Council of Science (Grant no. 673/2014).

applications with lower step-up or step-down ratio, a common solution is a non-isolated type [14]–[16]. As compared to isolated converters, it provides high efficiency, high power density, and smaller size and lower cost.

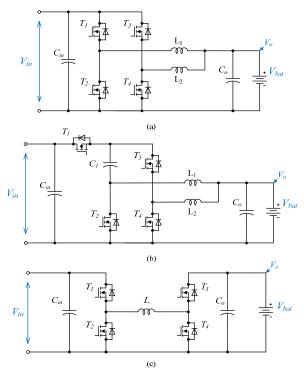

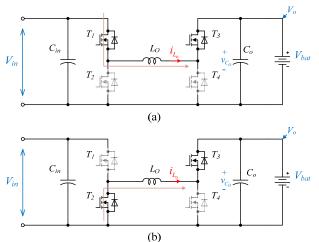

Figure 1 compares non-isolated topologies: interleaved topologies (Fig. 1(a) and Fig. 1(b)) and a cascaded topology (Fig. 1(c)). In those topologies, hard switching control limits their efficiency. Commonly, to overcome that problem and exploit the benefits of Zero-Voltage-Switching (ZVS) or Zero-Current-Switching (ZCS), auxiliary circuitry is used. Resonant switching increases efficiency by reducing switching losses; however, it increases the size, cost, complexity and makes tuning more difficult. Other options are special modulation techniques or increasing the frequency and using the parasitic element of the device as resonant elements (e.g. FETs output capacitance  $C_{oss}$ ). Still, switching limitation of traditionally used Si MOSFETs lies in the range of couple hundreds of kilohertz, which usually is insufficient.

A solution to this problem can be the use of transistor hetero structures as AlGaN/GaN-based advanced materials. Unique properties of these semiconductors (wide band gap, high values of the charge carrier mobility and saturation velocity, high coefficient of thermal conductivity, etc.) have led to the emergence of devices that have record values of power, voltage and current, as well as the operating frequency (1 MHz–2 MHz) [17]–[20]. High switching frequency allows using extremely small passive elements. At the same time, according to [18], losses in the passive elements are becoming more critical and are limiting the switching frequency.

References [21], [22] illustrate the relations of the switching loss and show some important power losses characteristics. Figure 22 in [21] and Fig. 17 in [22] clearly show that the main contribution in total losses of transistors (especially during ZVS/ZCS switching) are made by conduction losses. Thus, topologies with minimum conduction losses are preferable for further investigations.

This paper provides a comparative analysis of the proposed bidirectional topologies with criteria related to passive volume, voltage stress on semiconductors and conduction losses, to choose a better structure for low-medium power portable applications.

Fig. 1. Proposed topologies for the comparative analysis: a) two-phase interleaved; b) two-phase interleaved charge-pump; c) cascaded.

## II. CRITERIA FOR COMPARATIVE ANALYSIS OF CONVERTER TOPOLOGIES

This section describes the criteria used for the comparative analysis of the presented topologies.

Evaluation criteria are chosen based on the consideration that the topology should have minimum conduction losses, minimum voltage stress on the semiconductor devices and minimum size of passive components [23]–[30]. The main estimated values here should be represented in relative units (p.u.) to neglect the effect of input/output parameters for final comparison. Also, the analysis is made for one power flow direction (buck operating mode) only at constant output power.

To estimate the contribution of power switches, the value of total voltage stress is taken into consideration as one of the criteria

$$T_W = \sum_{i=1}^{N_T} V_{Ti},$$

(1)

where  $N_T$  is the number of transistors. The amount of power diodes blocking voltage  $D_W$  is not taken into account because all the presented topologies use synchronous rectifications (diodes connected in parallel with switches), as a result,  $T_W \cong D_W$ .

Conduction losses in semiconductors are expressed as

$$P_{CL} = \sum_{i=1}^{N_T} I_{RMSi}^2 \times R_{DSoni}, \qquad (2)$$

where  $I_{RMSi}$  is RMS current through the transistor,  $R_{DSoni}$  – drain-source on resistance.

Conduction losses include the sum of power transistors and diodes conduction losses:  $P_{CL} = P_{TC} + P_{DC}$ . But due to synchronous rectification, diodes will be conducted only during the dead time between the control signals. This amount of losses can be neglected without a serious impact on the final calculation results. Thus,  $P_{CL} \cong P_{TC}$ .

Based on our hypothesis, the relative size of inductors and capacitors is proportional to the stored energy, so maximum energy stored in the inductors is

$$Vol_L \cong E_{LW} = \sum_{i=1}^{N_L} \frac{L_i I_{AVi}^2}{2},$$

(3)

where  $N_L$  is the number of inductances in the topology,  $I_{AV}$  – average current through the inductor.

Maximum energy stored in the output capacitor

$$Vol_C \cong E_{CW} = \frac{CV_{AV}^2}{2},\tag{4}$$

where  $V_{AV}$  – average voltage on the capacitor.

#### III. ANALYSIS OF THE BIDIRECTIONAL CONVERTERS

#### A. Two-Phase Interleaved Bidirectional DC-DC Converter

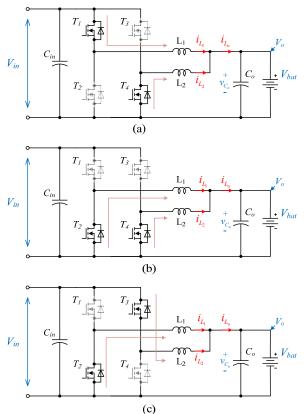

The concept of the half-bridge interleaved bidirectional DC-DC converter is proposed and described in [22], [31]–[39]. Figure 2 shows the basic operational modes of an interleaved two-phase converter during the buck state.

Fig. 2. Two-phase interleaved bidirectional converter in operational mode 1 (a); in mode 2,4 (b); in mode 3 (c).

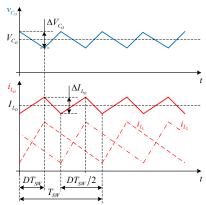

Linear-ripple approximated waveforms of inductor

currents and output capacitor voltage are shown in Fig. 3. Assuming that the scheme works in the continuous conduction mode (CCM), the dependence between the input DC voltage  $V_{IN}$  and the output voltage  $V_O$  will be

$$V_O = D \times V_{IN}, \tag{5}$$

where *D* is duty cycle.

By means of power balance and assuming an ideal converter (energy conversion efficiency  $\eta = 100\%$ ), an average output current can be represented as:

$$P_{IN} \approx P_O = V_O \times I_O, \tag{6}$$

$$I_O = \frac{P_O}{V_O},\tag{7}$$

where  $P_{IN}$  and  $P_{OUT}$  are input and output power respectively. Assuming that the topology phases are equally loaded, the output dc current in each inductor will be

$$I_{L_1} = I_{L_2} = \frac{P_O}{2 \times I_O}. (8)$$

Fig. 3. Capacitor voltage and inductor current waveforms of two-phase interleaved topology.

Inductor current ripple is represented as

$$\Delta I_{L_{1}} = \int_{0}^{DT_{SW}} \frac{di_{L_{1}}}{dt} dt = \frac{(V_{IN} - V_{O})}{L_{1}} \times D \times T_{SW}.$$

(9)

Inductance  $L_1$  can be represented by well-known formulas [39], but in our case, it is better to express it through the current ripple factor

$$K_{L_{1}} = \frac{\Delta I_{L_{1}}}{I_{L_{1}}} = \frac{2 \times V_{O} \times (V_{IN} - V_{O})}{L_{1} \times P_{O}} D \times T_{SW}.$$

(10)

Thus, inductance is expressed as

$$L_{1} = L_{2} \ge \frac{2 \times V_{O}^{2} \times (V_{IN} - V_{O})}{V_{IN} \times K_{L_{1}} \times P_{O}} T_{SW}. \tag{11}$$

A reference condition for calculating relative units for all topologies will be  $V_O = V_{IN}/8$ . This value is chosen to avoid

border conditions and due to schematic limitations of the second topology where the duty cycle D can be only in the range 0...0.5 and the output voltage cannot be higher than  $V_{IN}/4$  [40], [41].

Assume that the condition  $V_O = V_{IN}/8$  corresponds to one relative unit of the inductance, thus

$$L = \frac{7 \times V_{IN}^2 \times T_{SW}}{256 \times K_{L_1} \times P_O} = 1 \, p.u. \tag{12}$$

Inductance is expressed as

$$L_1 = L_2 = L \times \frac{512 \times V_O^2 \times (V_{IN} - V_O)}{7 \times V_{IN}^3}.$$

(13)

Average voltage on the output capacitor equals  $V_O$

$$V_{C_O} = V_O. (14)$$

Due to a ripple cancellation effect on the interleaved converters, the ripple voltage behavior of the capacitor differs slightly from the conventional buck converter. Rearranging the equations for the capacitor volt-second balance and the capacitor electrical charge [31],  $C_O$  voltage ripple is evaluated as (Fig. 3)

$$\Delta V_{C_O} = \frac{1}{C_O} \int_0^{DT_{SW}} i_{C_O}(t)dt =$$

$$= \frac{P_O \times (1 - 2 \times D) \times D}{V_O \times C_O} \times D \times T_{SW}. \tag{15}$$

Output capacitor voltage ripple factor is expressed as

$$K_{C_O} = \frac{\Delta V_{C_O}}{V_{C_O}} = \frac{P_O \times (1 - 2 \times D) \times D}{V_O^2 \times C_O} \times D \times T_{SW}. \quad (16)$$

It should be noted that in (15) the coefficient that affects ripple cancellation  $(1-2\cdot D)\cdot D$  is correct only for  $D\leq 0.5$ . For the value D>0.5, this coefficient should be  $(1-2\cdot D')\cdot D'$ , where D'=1-D. Thus, the output capacitance value is

$$C_{O} = \begin{cases} \frac{P_{O} \times (1-2 \times D) \times D}{V_{O}^{2} \times K_{C_{O}}} D \times T_{SW}, & for \ D \leq 0.5, \\ \frac{P_{O} \times (1-2 \times D') \times D'}{V_{O}^{2} \times K_{C_{O}}} D \times T_{SW}, & for \ D > 0.5. \end{cases}$$

(17)

For the condition  $V_O = V_{IN}/8$ , one capacitance relative unit is

$$C = \frac{3 \times P_O \times T_{sw}}{4 \times V_{IN}^2 \times K_{CO}} = 1 \, p.u.$$

(18)

Output capacitance is expressed as

$$C_{O} = \begin{cases} C \times \frac{4}{3} \times \left(1 - 2 \times \frac{V_{O}}{V_{IN}}\right), & \text{for } D \leq 0.5, \\ C \times \frac{4}{3} \times \frac{\left(2 \times V_{O} - V_{IN}\right) \times \left(1 - \frac{V_{O}}{V_{IN}}\right)}{V_{O}}, & \text{for } D > 0.5. \end{cases}$$

(19)

Based on Fig. 2, maximum voltage stress on each power switch is

$$V_{T1..T4} = V_{IN}. (20)$$

## B. Two-Phase Interleaved Bidirectional DC-DC Charge-Pump Converter

Since for the previous topology, general calculation principles are used, for the second topology, equations will be expressed in a similar manner.

Due to the phase switches  $T_I$  and  $T_3$  connected in series, it can be clearly seen from Fig. 4 that in the buck mode, the duty cycle of the control signals cannot be equal or greater than 0.5 [40]–[46]. Dependence between the input DC voltage  $V_{IN}$  and the output voltage  $V_O$  will be

$$V_O = \frac{D \times V_{IN}}{2}. (21)$$

As in the previous topology (7), assume that current sharing is ideal, so the inductor DC-current is

$$I_{L_1} = I_{L_2} = \frac{P_O}{2 \times V_O}. (22)$$

For further calculations, the value of the voltage on the charge-pump capacitor  $C_1$  is needed. It can be expressed from the equation system for inductor volt-second balance [42], [46]:

$$\begin{cases} D \times (V_{IN} - V_O - v_{C_1}) + (1 - D) \times (-V_O) = 0, \\ D \times (v_{C_1} - V_O) + (1 - D) \times (-V_O) = 0. \end{cases}$$

(23)

The obtained capacitor voltage is  $v_{C_1} = V_{IN}/2$ . Assuming that the capacitor  $C_I$  is large enough, the voltage  $v_{C_1}$  is considered the same during the whole switching period.

Inductor current ripple is

$$\Delta I_{L_{1}} = \frac{(V_{IN} - V_{O} - v_{C_{1}})}{L_{1}} \times D \times T_{SW} = \frac{(V_{IN} - V_{O})}{L_{1}} \times D \times T_{SW}.$$

(24)

Current ripple factor for one phase is

$$K_{L_{1}} = \frac{\Delta I_{L_{1}}}{I_{L_{1}}} = \frac{4 \times V_{O}^{2} \times (\frac{V_{IN}}{2} - V_{O})}{V_{IN} \times L_{1} \times P_{O}} T_{SW}.$$

(25)

Fig. 4. Two-phase interleaved bidirectional charge-pump converter in operation mode 1 (a); in mode 2,4 (b); in mode (3).

Thus, phase inductance can be expressed as

$$L_{1} = L_{2} \ge \frac{4 \times V_{O}^{2} \times (\frac{V_{IN}}{2} - V_{O})}{V_{IN} \times K_{L_{1}} \times P_{O}} T_{SW}.$$

(26)

For the condition  $V_O = V_{IN}/8$ , one inductance relative unit is

$$L = \frac{3 \times V_{IN}^2 \times T_{SW}}{128 \times K_{L_1} \times P_O} = 1 \, p.u. \tag{27}$$

The equation for inductance expressed in relative units is

$$L_{1} = L_{2} = L \times \frac{512 \times V_{O}^{2} \times \left(\frac{V_{IN}}{2} - V_{O}\right)}{3 \times V_{IN}^{3}}.$$

(28)

Based on equations from [40]-[42], the output capacitor voltage ripple is

$$\Delta V_{CO} = \frac{1}{C_O} \int_0^{DT_{SW}} i_{C_O}(t) dt =$$

$$= \frac{P_O \times (0.5 - D) \times D}{V_O \times C_O} \times D \times T_{SW}. \tag{29}$$

Taking into account that an average output capacitor voltage should be constant, the voltage ripple factor is

$$K_{C_O} = \frac{\Delta V_{C_O}}{V_{C_O}} = \frac{P_O \times (0.5 - D) \times D}{V_O^2 \times C_O} \times D \times T_{SW}.$$

(30)

The equation for the output capacitor is expressed as

$$C_O = \frac{P_O \times (0.5 - D) \times D}{V_O^2 \times K_{C_O}} \times D \times T_{SW}.$$

(31)

Based on the condition  $V_O = V_{IN}/8$ , one relative unit of the capacitance is

$$C = \frac{P_O \times T_{SW}}{V_{IN}^2 \times K_{CO}} = 1 \, p.u. \tag{32}$$

Thus, the equation for the output capacitance is

$$C_O = C \times \left(2 - 2 \times D\right) = C \times \left(2 - \frac{8 \times V_O}{V_{IN}}\right). \tag{33}$$

From Fig. 4, the total voltage stress on the semiconductors is:

$$\begin{cases} V_{T1} = V_{T2} = V_{T4} = \frac{V_{IN}}{2}, \\ V_{T3} = V_{IN}. \end{cases}$$

(34)

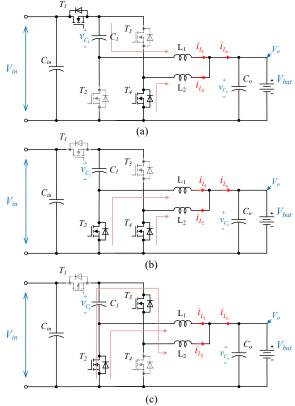

#### C. Cascaded Bidirectional DC-DC Converter

The most universal solution for a bidirectional power flow interface is a cascaded converter [47]–[59]. This topology can provide either step-up or step-down conversion in both directions.

Control strategies for the cascaded converter can vary. There are some modulation techniques that allow achieving ZVS and thus obtain better efficiency [47]–[49]. To simplify the calculations, a simple buck mode will be used: switch  $T_1$  acts as the main power switch,  $T_2$  operates as the main diode,  $T_3$  is always open [55], [57]–[59]. Figure 5 shows basic operation modes of the cascaded converter.

Fig. 5. Cascaded bidirectional converter in operation mode 1 (a) and 2 (b).

The relation between the input and the output voltage in CCM is the same as for a conventional buck converter

$$V_O = D \times V_{IN}. \tag{35}$$

Average current in the inductor is

$$I_{L_O} = \frac{P_O}{I_O}. (36)$$

Inductor current ripple is represented as

$$\Delta I_{L_O} = \int_{0}^{DT_{SW}} \frac{di_{L_O}}{dt} dt = \frac{(V_{IN} - V_O)}{L_O} D \times T_{SW}.$$

(37)

As for the previous two topologies, inductance is calculated through relative units:

$$K_{L_O} = \frac{\Delta I_{L_O}}{I_{L_O}} = \frac{V_O^2 \times (V_{IN} - V_O)}{L_O \times P_O \times V_{IN}} T_{SW},$$

(38)

$$L_O \ge \frac{V_O^2 \times (V_{IN} - V_O)}{V_{IN} \times K_{L_O} \times P_O} T_{SW}, \tag{39}$$

$$L = \frac{7 \times V_{IN}^2 \times T_{SW}}{512 \times K_{L_O} \times P_O} = 1 \, p.u., \tag{40}$$

$$L_O = L \times \frac{512 \times V_O^2 \times (V_{IN} - V_O)}{7 \times V_{IN}^3}.$$

(41)

Assuming that the output capacitor voltage ripple changes linearly, the output capacitor in relative units is represented as:

$$\Delta V_{C_O} = \frac{1}{C_O} \int_0^{DT_{SW}} i_{C_O}(t) dt =$$

$$= \frac{P_O \times (1 - D) \times D}{V_O \times C_O} \times D \times T_{SW}, \tag{42}$$

$$K_{C_O} = \frac{\Delta V_{C_O}}{V_{C_O}} = \frac{P_O \times (1 - D) \times D}{V_O^2 \times C_O} \times D \times T_{SW},$$

(43)

$$C_O = \frac{P_O \times (1 - D) \times D}{V_O^2 \times K_{C_O}} \times D \times T_{SW}, \tag{44}$$

$$C = \frac{7 \times P_O \times T_{SW}}{8 \times V_{IN}^2 \times K_{C_O}} = 1 \text{ p.u.}, \tag{45}$$

$$C_O = C \times \frac{8}{7} \times (1 - D) = C \times \frac{8}{7} \times \left(1 - \frac{V_O}{V_{IN}}\right).$$

(46)

Maximum transistor voltages are:

$$\begin{cases} V_{T1} = V_{T2} = V_{IN}, \\ V_{T3} = 0, \\ V_{T4} = V_{O}. \end{cases}$$

(47)

## IV. SUMMARIZED COMPARATIVE ANALYSIS OF THE SELECTED TOPOLOGIES

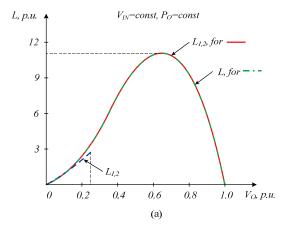

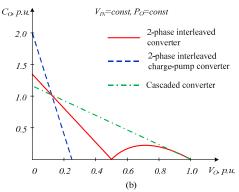

To sum up the calculation results from Section III, the criteria are used for comparison in all topologies mentioned above. Figure 6 shows the curves for passive elements estimated in relative units, as a function of output voltage. Final formulas are received for the CCM operation mode based on (1)–(4) and placed in Table I. Radar diagrams

depicted in Fig. 7 are built at constant output power by using such formulas for three different cases:  $V_O = 0.1 \cdot V_{IN}$ ,  $V_O = 0.2 \cdot V_{IN}$ , and  $V_O = 0.4 \cdot V_{IN}$ .

It should be noted that the length of different spokes  $(T_W, P_{CL}, E_{LW}, \text{ and } E_{CW})$  reflects normalized calculated data.

No diagram for an interleaved charge-pump converter is shown in Fig. 7(c) because of the limitations described above.

Fig. 6. Comparison of passive elements: inductance (a); output capacitance (b).

The comparative analysis showed that the characteristics of conduction losses, the volume of inductive components and the capacitor typical of a cascaded converter are worse than those of other topologies analysed in the paper. As compared to a similar charge-pump topology, the two-phase interleaved bidirectional DC-DC converter has larger total voltage stress on power switches, whereas the conduction losses and the volume of the inductor are similar.

Fig. 7. Comparative analysis in terms of weighted criteria at constant output power: for  $V_{OUT} = 0.1 \cdot V_{IN}$  (a); for  $V_{OUT} = 0.2 \cdot V_{IN}$  (b); for  $V_{OUT} = 0.4 \cdot V_{IN}$  (c).

TABLE I. SUMMARIZED COMPARISON RESULTS AT CONSTANT OUTPUT POWER.

|                                                 | Topologies                                                                                       |                                                                                                                   |                                                                                         |

|-------------------------------------------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| Criteria                                        | Two-phase interleaved bidirectional converter (Fig. 1(a))                                        | Two-phase interleaved bidirectional charge-<br>pump converter (Fig. 1(b))                                         | Cascaded bidirectional converter (Fig. 1(c))                                            |

| Total voltage stress                            | $T_W = 4 \times V_{IN}$                                                                          | $T_W = 2,5 \times V_{IN}$                                                                                         | $T_W = 2 \times V_{IN} + V_O$                                                           |

| Conduction losses                               |                                                                                                  | $P_{CL} = (2+D) \times \left(I_{L_1}^2 + \frac{\Delta I_{L_1}^2}{12}\right) \times R_{DSon}$                      |                                                                                         |

| Maximum<br>energy stored<br>in the<br>inductors | $E_{LW} = 2 \times L \times \frac{64 \times P_O^2 \times (V_{IN} - V_O)}{7 \times V_{IN}^3}$     | $E_{LW} = 2 \times L \times \frac{64 \times P_O^2 \times \left(\frac{V_{IN}}{2} - V_O\right)}{3 \times V_{IN}^3}$ | $E_{LW} = L \times \frac{256 \times P_O^2 \times (V_{IN} - V_O)}{7 \times V_{IN}^3}$    |

| Maximum<br>energy stored<br>in the<br>capacitor | $E_{CW} = C \times \frac{2 \times \left(1 - 2 \times \frac{V_O}{V_{IN}}\right) \times V_O^2}{3}$ | $E_{CW} = C \times \frac{\left(2 - 8 \times \frac{V_O}{V_{IN}}\right) \times V_O^2}{2}$                           | $E_{CW} = C \times \frac{4 \times \left(1 - \frac{V_O}{V_{IN}}\right) \times V_O^2}{7}$ |

On the other hand, a charge-pump converter has a limitation because its output voltage cannot exceed  $V_{IN}/4$ . It restricts the use of such topology in real applications. In the context of further work, the results obtained will be used to choose an appropriate converter topology for low-medium power portable applications.

## V. BIDIRECTIONAL DC-DC INTERLEAVED CONVERTER EXPERIMENTAL PROTOTYPE

To verify the proposed comparison method, the models of two converters were analysed in PSIM software. Two-phase interleaved charge pump topology was eliminated due to the limitation on the input to the output voltage relationship. Therefore, models of two-phase interleaved and cascaded topologies were studied in charge and discharge modes with DC-link voltage 12 V and battery voltage 7.2 V. It was concluded that the results observed have a very good correlation with those theoretically received.

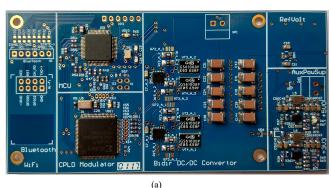

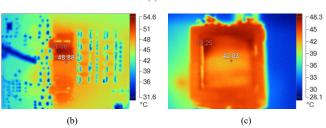

Finally, the conventional bidirectional interleaved DC-DC converter was accepted as the best solution. Figure 8 shows the developed 100 W prototype (top view) along with thermal images.

GaN-based transistors GS61008P from GaN Systems were used as a switching device in the experimental prototype. The power source chosen was 2 series connected LiFePO<sub>4</sub> 18650 cells from A123 Systems with a cutoff voltage from 2 V till 3.6 V and nominal voltage 3.3 V. Prototype parameters are presented in Table II. To reduce conduction losses and decrease overall volume, custommade inverse coupled inductors were used. The control system is a combination of MCU (STM32F410R8) for data processing and control and CPLD (XC2C256-7VQ100C) for high-frequency PWM generation.

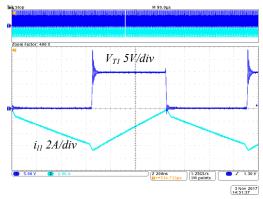

Switching frequency of the two cases was tested: 500 kHz and 800 kHz. Figure 9 shows the voltage and current diagrams across the transistor and the inductor, correspondingly. It should be noted that the voltage spike across the GaN transistors is present. It can be explained by zero deadtime set in the control system in order to minimize conduction losses of GaN transistors.

TABLE II. PARAMETERS OF THE EXPERIMENTAL PROTOTYPE.

| Parameter                             | Value    |

|---------------------------------------|----------|

| Input voltage, $V_{IN}$               | 47.2 V   |

| Output voltage, $V_O$                 | 12 V     |

| Maximum input current, $I_{IN}$       | 15 A     |

| Maximum output power, $P_{Omax}$      | 100 W    |

| Switching frequency, $f_{SW}$         | 500 kHz  |

| Magnetic inductance, $L_S$            | 350 nH   |

| Coupling coefficient,                 | -0.4     |

| Input/output capacitors, $C_{IN}/C_O$ | 110 μF   |

| GaN transistors                       | GS61008P |

| Transistor drivers                    | LM5113   |

Fig. 8. Developed 100 W prototype (top view) of the bidirectional interleaved converter (a) and thermal images under full load condition transistors (b), an inductor (c).

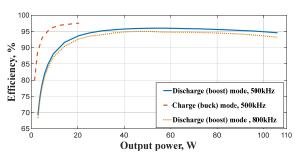

To estimate total power losses in the converter and prove the right choice of the topology, efficiency was measured by the precision power analyser Yokogawa WT1800 (Fig. 10).

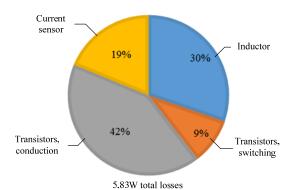

Rough total losses distribution in the converter during maximum load operation is illustrated in Fig. 11. It should be noted that the efficiency analysis does not include losses in the control system, which are about 0.54 W. Conduction losses were calculated using the measured current, the duty cycle and the on-state transistor resistance obtained from the datasheet.

Fig. 9. Voltage waveform across the transistor and current waveform across the inductor.

Resistive-based current sensor losses were measured in the same way. Calculation of the switching losses of the transistor was obtained using the numerical values from the transistor datasheet and measured by the oscilloscope Tektronix MSO4043B with passive probes and current probe Tektronix TCP0030A with a bandwidth no less than 100 MHz. Coupled inductor losses were found by subtracting losses of the switches and the current sensor from the total losses. Obtained results were verified with the help of temperature analysis measured by a thermal imaging camera Fluke Ti10. Theoretically, received results show good correlation with those of the thermal analysis.

Fig. 10. Overall efficiency of the two-phase interleaved bidirectional converter.

Fig. 11. Power losses distribution in the converter at maximum load.

#### VI. CONCLUSIONS

This paper proposes comprehensive comparative analysis in order to define the optimal topology for the bidirectional DC-DC converter for low power energy storage applications. Focus in the analysis was concentrated on four parameters: conduction losses, voltage stress, the volume of inductive, and capacitance elements (reflected by maximum energy stored in such components).

Based on proposed approach it is shown that a conventional bidirectional buck-boost interleaved converter can be considered as one of the most suitable solutions. In addition, it was experimentally proven that in combination with modern semiconductor devices, very high efficiency and power density can be achieved.

#### REFERENCES

- "Renewables 2016 Global Status Report", Renewable Energy Policy Network for the 21st Century, Paris, France, March, 2016.

- [2] "Global EV outlook 2016, Beyond one million electric cars", International Energy Agency, Paris, France, May, 2016.

- [3] "Evolution, Electric Vehicles in Europe: gearing up for a new phase?", Amsterdam Roundtable Foundation and McKinsey & Company, the Netherlands, Amsterdam, Netherland, April, 2014.

- [4] M. Singer, "Consumer View on Plug-in Electric Vehicles National Benchmark Report", National Renewable Energy Laboratory, USA, January, 2016.

- [5] K. H. Solangi, M. R. Islam, R. Saidur, N. A. Rahim, H. Fayaz, "A review on global solar energy policy", *Renewable and Sustainable Energy Reviews*, vol. 15, pp. 2149–2163, 2011. DOI: 10.1016/j.rser.2011.01.007

- [6] "The Future of Solar Energy", Energy Initiative Massachusetts Institute of Technology, 2015.

- [7] "Photovoltaics Report", Fraunhofer Institute for Solar Energy Systems, Freiburg, Germany, Oct., 2016.

- [8] M. Pagliaro, R. Ciriminna, G. Palmisano, "Flexible solar cells", *ChemSumChem* 2008, pp. 880–891, 2008. DOI: 10.1002/9783527623808.

- [9] S. R. Kodigala, *Thin film solar cells from earth abundant materials*. London: Elsevier, 2014.

- [10] K. L. Chopra, "Thin film solar cells (a status review)", Laboratory for Thin Films and Photovoltaics, 2010.

- [11] A. K. Widiawan, R. Tafazolli, "High altitude platform station (HAPS): A review of new infrastructure development for future wireless communications", Wireless Personal Communications, vol. 42, pp. 387–404, 2007. DOI: 10.1007/s11277-006-9184-9.

- [12] K. Trautz, P. Jenkins, R. Walters, D. Scheiman, R. Hoheisel, "High efficiency flexible solar panels", in *Proc.* 39<sup>th</sup> IEEE Photovoltaic Specialista Conf., 2013, pp. 115–119. DOI: 10.1109/PVSC.2013.6744111.

- [13] D. Scheiman, P. Jenkins, R. Walters, K. Trautz, R. Hoheisel, R. Tatavarti, "High efficiency flexible triple junction solar panels", in *Proc.* 40th IEEE Photovoltaic Spec. Conf., 2014, pp. 1376–1380. DOI: 10.1109/PVSC.2014.6925174.

- [14] K. Tytelmaier, O. Husev, O. Veligorskyi, R. Yershov, "A review of non-isolated bidirectional DC-DC converters for energy storage systems", in *Proc. II Int. Young Scientists Forum on Applied Physics* and Engineering, 2016, pp. 1–7. DOI: 10.1109/YSF.2016.7753752.

- [15] Q. Xu, T. Cai, Y. Liu, L. Yao, P. Zeng, "Location planning of charging stations for electric vehicles based on drivers behaviours and travel chain", *Automation of Electric Power Systems*, vol. 40, pp. 59– 65, 2016..

- [16] N. B. Dawood, "Review of different DC to DC converters based for renewable energy applications", *International Research Journal of Engineering and Technology*, vol. 3, no. 3, pp. 46–50, 2016.

- [17] A. Lidow, "GaN transistors giving new life to Moore's law", in Proc. IEEE 27th Int. Symposium on Power Semiconductor Devices & IC's (ISPSD 2015), Hong Kong, China, 2015, pp. 1–5. DOI: 10.1109/ISPSD.2015.7123375.

- [18] J. Kolar, D. Bortis, D. Neumayr, "The ideal switch is not enough", in Proc. of IEEE 28th Int. Symposium on Power Semiconductor Devices and ICs (ISPSD 2016), Prague, Czech Republic, 2016, pp. 15–22. DOI: 10.1109/ISPSD.2016.7520767.

- [19] M. Danilovic, Z. Chen, R. Wang, F. Luo, "Evaluation of the switching characteristics of a gallium-nitride transistor", in *Proc.*

- IEEE Energy Conversion Congress and Exposition (ECCE 2011), Phoenix, AZ, USA, 2011, pp. 2681–2688. DOI: 10.1109/ECCE.2011.6064128.

- [20] D. Reusch, J. Strydom, "Evaluation of Gallium Nitride transistors in high frequency resonant and soft-switching DC-DC converters", *IEEE Trans. Power Electr.*, vol. 30, no. 9, pp. 5151–5158, 2015. DOI: 10.1109/TPEL.2014.2364799.

- [21] X. Huang, Q. Li, Z. Liu, F. C. Lee, "Analytical loss model of high voltage GaN HEMT in cascade configuration", *IEEE Trans. Power Electronics*, vol. 29, no. 5, pp. 2208–2219, 2014. DOI: 10.1109/TPEL.2013.2267804.

- [22] X. Huang, F. C. Lee, Q. Li, W. Du, "High-frequency high-efficiency GaN-based interleaved CRM bidirectional buck/boost converter with inverse coupled inductor", *IEEE Trans. Power Electronics*, vol. 31, no. 6, pp. 4343–4352, 2015. DOI: 10.1109/TPEL.2015.2476482.

- [23] O. Husev, F. Blaabjerg, C. Roncero-Clemente, E. Romero-Cadaval, D. Vinnikov, Y. P. Siwakoti, R. Strzelecki, "Comparison of impedance-source networks for two and multilevel buck-boost inverter applications", *IEEE Trans. Power Electronics*, vol. 31, no. 11, pp. 7564–7579, 2016. DOI: 10.1109/TPEL.2016.2569437.

- [24] D. Panfilov, O. Husev, F. Blaabjerg, J. Zakis, K. Khandakji, "Comparison of three-phase three-level voltage source inverter with intermediate dc-dc boost converter and quasi-Z-source inverter", *IET Power Electronics*, vol. 9, no. 6, pp. 1238–1248, 2016. DOI: 10.1049/iet-pel.2015.0539.

- [25] T. E. Shults, O. O. Husev, J. G. Zakis, "Overview of impedance source networks for voltage source inverters", in *Proc. 16<sup>th</sup> Int. Conf. Micro/Nanotechnologies and Electron Devices*, Erlagol, Russia, 2015, pp. 514–520. DOI: 10.1109/EDM.2015.7184596.

- [26] A. Battiston, J.-P. Mattin, E.-H. Miliani, B. Nahid-Mobarakeh, S. Pierfederici, F. Meibody-Tabar, "Comparison criteria for electronic traction system using Z-source inverter and conventional architectures", *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 2, no. 3, pp. 467–476, 2014. DOI: 10.1109/JESTPE.2014.2298755.

- [27] M. Shen, A. Joseph, J. Wang, F. Z. Peng, D. J. Adams, "Comparison of traditional inverters and Z-source inverter for fuel cell vehicles", *IEEE Trans. Power Electronics*, vol. 22, no. 4, pp. 1453–1463, 2004. DOI: 10.1109/TPEL.2007.900505.

- [28] A. M. Roldan, A. Barrado, J. Pleite, J. Vazquez, E. Olias, "Size and cost reduction of the energy-storage capacitors", in *Proc. 19th Annual IEEE Applied Power Electronics Conf. and Exposition*, 2004, pp. 723–729. DOI: 10.1109/APEC.2004.1295899.

- [29] J. Kolar, U. Drofenik, J. Biela, M. Heldwein, H. Ertl, T. Friedli, S. Round, "PWM converter power density barriers", *IEEJ Trans. Industry Applications*, vol. 128, no. 4, pp. 9–29, 2007. DOI: 10.1109/PCCON.2007.372914.

- [30] W. T. Franke, M. Mohr, F. W. Fuchs, "Comparison of a Z-source inverter and a voltage-source inverter linked with a DC/DC-boost-converter for wind turbines concerning their efficiency and installed semiconductor power", in *Proc. Power Electronics Specialists Conf.*, Rhodes, Greece, 2008, pp. 1814–1820. DOI: 10.1109/PESC.2008.4592207.

- [31] J.-P. Lee, H. Cha, D. Shin, K.-J. Lee, D.-W. Yoo, J.-Y. Yoo, "Analysis and design of coupled inductors for two-phase interleaved DC-DC converter", *Journal of Power Electronics*, vol. 13, no. 3, pp. 339–348, 2013. DOI: 10.6113/JPE.2013.13.3.339.

- [32] G.-Y. Choe, J.-S. Kim, H.-S. Kang, B.-K. Lee, "An optimal design methodology of an interleaved boost conveter for fuel cell applications", *Journal of Electrical Engineering & Technology*, vol. 5, no. 2, pp. 319–328, 2010. DOI: 10.5370/JEET.2010.5.2.319.

- [33] J.-B. Baek, W.-I. Choi, B.-H. Cho, "Digital adaptive frequency modulation for bidirectional DC-DC converter", *IEEE Trans. Industrial Electronics*, vol. 60, no. 11, pp. 5167–5176, 2013. DOI: 10.1109/TIE.2012.2224075.

- [34] Y. Yugang, Y. Dong, F. C. Lee, "A new coupled inductors design in 2-phase interleaved VRM", in *Proc. IEEE 6<sup>th</sup> Int. Power Electronics* and Motion Control Conf., 2009, pp. 344–350. DOI: 10.1109/IPEMC.2009.5157410.

- [35] E.-C. Nho, J.-H. Jung, H.-S. Kim, I.-D. Kim, H.-G. Kim, T.-W. Chun, "Switching loss minimization of 3-phase interleaved bidirectional DC-DC converter", in *Proc. 2014 Int. Power Electronics Conf.* (IPEC-Hiroshima 2014 - ECCE ASIA), Hiroshima, Japan, 2014, pp. 1–5. DOI: 10.1109/IPEC.2014.6870072.

- [36] W. Yu, H. Qian, J.-S. Lai, "Design of high-efficiency bidirectional DC-DC converter and high-precision efficiency measurement", in Proc. 34th Annual Conf. IEEE Industrial Electronics, Orlando, FL, USA, 2008, pp. 685–690. DOI: 10.1109/IECON.2008.4758036.

- [37] J. Zhang, J.-S. Lai, W. Yu, "Bidirectional DC-DC converter modeling and unified controller with digital implementation", in *Proc.* 23<sup>rd</sup>

- Annual IEEE Applied Power Electronics Conf. and Exposition, Austin, TX, USA, 2008, pp. 1747–1753. DOI: 10.1109/APEC.2008.4522963.

- [38] P. Nandankar, J. P. Rothe, "Design and implementation of efficient three-phase interleaved DC-DC converter", in *Int. Conf. & Workshop* on Electronics & Telecommunication Engineering (ICWET 2016), Mumbai, India, 2016, pp. 1–6. https://doi.org/10.1049/cp.2016.1114.

- [39] B. Hauke, "Basic calculation of a buck converter's power stage", Application Report SLVA477B – Dec. 2011 – Revised Aug. 2015.

- [40] C.-M. Lai, Y.-C. Lin, D. Lee, "Study and implementation of a two-phase interleaved bidirectional DC/DC converter for vehicle and DC-microgrid systems", *Energies 2015*, vol. 8, pp. 9969–9991, 2015. DOI: 10.3390/en8099969.

- [41] C.-M. Lai, "Development of a novel bidirectional DC/DC converter topology with high voltage conversion ratio for vehicles and DC-microgrids", *Energies* 2016, vol. 9, pp. 1–25, 2016. DOI: 10.3390/en9060410.

- [42] L.-K. Xue, P. Wang, Y.-F. Wang, T.-Z. Bei, H.-Y. Yan, "A four-phase high voltage conversion ratio bidirectional DC-DC converter for battery application", *Energies* 2015, vol. 8, pp. 6399–6426, 2015. DOI: 10.3390/en8076399.

- [43] A. Farooq, F. Ullah, M. Saleem, "Design of a novel voltage regulator module (VRM) with fast transient response", *International Journal of Computer Science Issues*, vol. 9, no. 2, pp. 54–61, 2012.

- [44] P. S. Krishna, E. P. Jubin, K. R. Hari, "Study and analysis of conventional and modified interleaved buck converter", *International Journal of Engineering Research and General Science*, vol. 3, no. 6, pp. 957–964, 2015.

- [45] J. Jose, M. K. Idikkula, "Design and MATLAB simulation of a fuel cell based interleaved buck converter with low switching losses and improved conversion ratio", *Journal of Electrical and Electronics Engineering*, vol. 7, no. 6, pp. 91–97, 2013. DOI: 10.9790/1676-0769197.

- [46] Y.-F. Wang, L.-K. Xue, C.-S. Wang, P. Wang, W. Li, "Interleaved high-conversion-ratio bidirectional DC-DC converter for distributed energy-storage systems – circuit generation, analysis and design", *IEEE Trans. Power Electronics*, vol. 31, no. 8, pp. 5547–5561, 2015. DOI: 10.1109/TPEL.2015.2496274.

- [47] S. Waffler, J. W. Kolar, "A novel low-loss modulation strategy for high-power bi-directional buck+boost conveters", in *Proc.* 7<sup>th</sup> Int. Conf. Power Electronics, Daegu, South Korea, 2007, pp. 889–894. DOI: 10.1109/ICPE.2007.4692513.

- [48] S. Waffler, J. W. Kolar, "Comparative evaluation of soft-switching concepts for bi-directional buck+boost Dc-Dc converters", in *Proc.* Int. Power Electronics Conf. (ECCE ASIA 2010), Sapporo, Japan,

- 2010, pp. 1856–1865. DOI: 10.1109/IPEC.2010.5542152.

- [49] K.-B. Liu, C.-Y. Liu, Y.-H. Liu, Y.-C. Chien, B.-S. Wang, Y.-S. Wong, "Analysis and controller design of a universal bidirectional DC-DC converter", *Energies* 2016, vol. 9, pp. 1–23, 2015. DOI: 10.3390/en9070501.

- [50] M. Rosekeit, P. Joebges, M. Lelie, D. U. Sauer, R. W. Doncker, "Undersampling control of a bidirectional cascaded buck+boost Dc-Dc converter", in *Proc. 2014 Int. Power Electronics Conf. (IPEC-Hiroshima 2014 - ECCE ASIA)*, Hiroshima, Japan, 2014, pp. 2729–2736. DOI: 10.1109/IPEC.2014.6869976.

- [51] M. Anun, M. Ordonez, I. Galiano, G. Oggier, "Bidirectional power flow with constant power load in electric vehicles: a non-linear strategy for buck+boost cascade converters", in *Proc. 29<sup>th</sup> Annual IEEE Applied Power Electronics Conf. Exposition (APEC 2014)*, Fort Worth, TX, USA, 2014, pp. 1697–1703. DOI: 10.1109/APEC.2014.6803534.

- [52] X. Zhang, Z. Wang, M. Cheng, S. Ding, W. Wang, "The random PWM based bi-directional buck-boost cascade converter for electric vehicles", in *Proc. Int. Conf. Electrical Machines and Systems*, Beijing, China, 2011, pp. 1–5. DOI: 10.1109/ICEMS.2011.6073802.

- [53] F. Caricchi, F. Crescimbini, F. G. Capponi, L. Solero, "Study of bi-directional buck-boost converter topologies for application in electrical vehicle motor drives", in *Proc. 13th Annual Applied Power Electronics Conf. Exposition*, Anaheim, CA, USA, USA, 1998, pp. 287–293. DOI: 10.1109/APEC.1998.647705.

- [54] S. Lale. M. Soja, S. Lubura, D. D. Mancic, M. D. Radmanovic, "A non-inverting buck-boost converter with an adaptive dual current mode control", *Electronics and Energetics*, vol. 30, no. 1, pp. 67–80, 2017. DOI: 10.2298/FUEE1701067L.

- [55] M. Green, "Design calculation for buck-boost converters", Application Report SLVA535A – August 2012 – Revised September 2012.

- [56] H. Fan, "Design tips for an efficient non-inverting buck-boost converter", Analog Application Journal, pp. 20–25, 2014.

- [57] H. Fan, "Four-switch buck-boost converter in buck or boost mode delivers the highest efficiency", EDN network, pp. 1–5, 2015.

- [58] S. C. Latha, N. Venugopal, C. J. Rao, "A positive buck boost converter with mode select circuit and feed forward techniques using fuzzy logic controller", *Int. Journal of Engineering Research and Applications*, vol. 4, no. 11, pp. 22–29, 2014.

- [59] S. C. Latha, N. Venugopal, "Performance of positive buck-boost converter with mode select circuit and feed-forward techniques using fuzzy logic controller", *International Journal on Resent and Innovation Trends in Computing and Communication*, vol. 3, no. 2, pp. 746–752, 2015. DOI: 10.17762/ijritcc2321-8169.150265.