# A Novel Super Transistor-Based High-Performance CCII and Its Applications

Leila Safari<sup>1</sup>, Shahram Minaei<sup>2</sup>

<sup>1</sup>Independent Researcher, Tehran, Iran <sup>2</sup>Department of Electronics and Communications Engineering, Dogus University, Acibadem, Istanbul, Turkey leilasafari@yahoo.com

Abstract-In this paper a high-performance low-voltage low-power CMOS second-generation current conveyor (CCII) is presented. The proposed CCII is based on super transistor (ST) and enables low input impedance at X terminal and high output impedance at Z terminal. It also utilizes a novel power saving strategy in which a single NMOS cascode current mirror conveys X terminal current to Z terminal, provides high impedance at Z terminal and reduces the X terminal impedance all together resulting in a low-power and compact structure. As another advantage, only NMOS transistors are used in processing voltage and current signals granting the proposed CCII high frequency operation. PMOS transistors are used only for biasing. However, the proposed CCII cannot provide infinite impedance at Y terminal. HSPICE simulations using 0.18 µm parameters and supply voltage of ±0.9 V confirms that the proposed CCII exhibits impedances of 0.155  $\Omega$ , 1.6 M $\Omega$  and 47 k $\Omega$  at X, Z and Y terminals, respectively. Voltage and current bandwidths are also 377 MHz and 159 MHz, respectively. Some of the applications of the proposed CCII are given.

*Index Terms*—Current-mode circuits; Analog integrated circuits.

# I. INTRODUCTION

In the last decade, current-mode (CM) signal processing has become very popular [1]–[20]. It provides innovative solutions to solve the problems of analog circuits in modern technologies and shows many advantages compared to conventional voltage-mode (VM) approach. Especially, current-mode technique allows realizing low-voltage, wide dynamic range and large bandwidth analog circuits and alleviates the problems of constant gain bandwidth product [1]–[20].

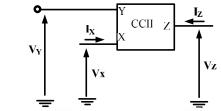

One of the most important current-mode building blocks is second-generation current conveyor (CCII) (Fig. 1) which finds many applications in implementing filters, instrumentation amplifiers, voltage and current amplifiers, oscillators etc. [3]–[14]. Moreover, having one high impedance input, one low impedance input and one high impedance output, it can operate in both current and voltage modes, which provides flexibility and enables variety of circuit designs.

The voltage applied to terminal Y of CCII is replicated to its X terminal. The current supplied to X terminal is conveyed to the high impedance output terminal Z with

Manuscript received 3 September, 2017; accepted 22 January, 2018.

either positive (CCII+) or negative polarities (CCII-). Therefore, X and Y terminals exhibit very low (ideally zero) and very high (ideally infinite) impedances, respectively. However non-ideal impedances at X and Z terminals and other parasitic elements limit the performance of CCII [19]. Furthermore, CCII's frequency performance directly determines the frequency performance of all circuits implemented with CCIIs. Consequently, a high-performance CCII (with high bandwidth, very low impedance at X terminal and very high impedance at Z terminal) are needed to improve the performance of CCII based circuits. However, the demand for low-voltage low-power operation [21] makes the design of such a high performance CCII very challenging.

Fig. 1. CCII symbol.

$$\begin{bmatrix} I_{Y} \\ \cdot \\ V_{X} \\ \cdot \\ I_{Z} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 \\ \beta & 0 & 0 \\ 0 & \pm \alpha & 0 \end{bmatrix} \begin{bmatrix} V_{Y} \\ \cdot \\ I_{X} \\ \cdot \\ V_{Z} \end{bmatrix}.$$

(1)

Literature survey shows that the previously reported are differential CCIIs mainly based on pair/transconductance and translinear topologies [3]-[4], [14], [15], [18], [22], [23]. In CCIIs made of differential pairs, a high gain negative feedback loop is used to reduce impedance at X terminal. In this approach, low impedance at X terminal, infinite impedance at Y terminal and wide frequency bandwidths (for both voltage and current signals) are achieved. However most of the CCIIs made of differential pair (or transconductance amplifier) topologies suffer from low impedance at Z terminal [3], [4], [12], [22]. Most importantly the impedance at X terminal starts to increase at frequencies much lower than voltage and current bandwidths. On the other hand, CCIIs based on translinear topology are not suitable for low voltage designs because they require large supply voltage of at least  $2V_{GS} + 2V_{DS}$ (with usual meaning of symbols) [15] and low impedance at X terminal is achievable at the cost of high power consumption. In addition, they suffer from low impedance at Z terminal and poor frequency performance because both P-type and N-type current mirrors are present in the signal path.

In this paper, a new topology to design high-performance CCII is proposed. The proposed topology is based on super transistor (ST) and enables very low input impedance and very low offset voltage at X terminal and high output impedance at Z terminal. Unlike differential pair topology, impedance at X terminal remains low even at high frequencies. The proposed topology includes an interesting power saving strategy in which a single NMOS cascode current mirror serves three functions simultaneously; it conveys X terminal current to Z output, provides high impedance at Z terminal and helps further reducing the X terminal impedance by establishing a negative feedback loop. Consequently, the proposed CCII enjoys a compact structure. As another advantage, only NMOS transistors are used in processing voltage and current signals granting the proposed CCII high frequency operation. However, similar to translinear based CCIIs, its impedance at Y terminal is not infinite. As application examples, the proposed CCII, is used in implementing a current-mode instrumentation amplifier, an electronically variable voltage amplifier and an electronically variable current amplifier. This paper is organized as follows: In Section II the proposed CCII circuit and its HSPICE simulation results using 0.18 µm TSMC CMOS technology are presented. Thereafter, CCII applications are discussed in Section III. The paper is concluded in Section IV.

# II. THE PROPOSED CCII

# A. Circuit Description

The proposed topology is based on STs which have been used in voltage-mode signal processing to improve the output resistance and linearity of source-degenerated differential CMOS transconductors [24]. In current-mode signal processing, they have been used to design a highperformance voltage feedback current amplifier [2].

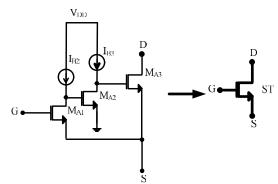

The implementation and symbol of a ST is shown in Fig. 2. It has three interesting characteristics making them highly suitable to design other current-mode building blocks especially CCIIs:

First, they exhibit very low input impedance at source terminal expressed as [24]

$$r_{s} \approx \frac{1}{g_{mA1}g_{mA2}g_{mA3}(r_{oA1}||r_{oIB2})(r_{oA2}||r_{oIB3})}$$

(2)

Second, they show high voltage tracking accuracy between gate and source terminals. Voltage gain between source and gate terminals is expressed as [24]

$$A_{v} = \frac{v_{s}}{v_{g}} \approx \frac{1}{1 + [g_{mA1}(r_{oA1} \| r_{oIB2}) g_{mA2}(r_{oA2} \| r_{oIB3})]^{-1}} \approx 1.$$

(3)

Third, the output impedance seen from their drain is very high and is described by [24]

$$\mathbf{r}_{d} \cong \mathbf{g}_{mA1}\mathbf{g}_{mA2}\mathbf{g}_{mA3}(\mathbf{R})(\mathbf{r}_{oA1}\|\mathbf{r}_{oIB2})(\mathbf{r}_{oA2}\|\mathbf{r}_{oIB3})(\mathbf{r}_{oA3}), \ (4)$$

where R is the equivalent resistance connected to the source node. In (2)–(4)  $g_m$  and  $r_o$  denote the transconductance and output impedance of the related transistor or current source, respectively.

Fig 2. Implementation and symbol of Super Transistor [24].

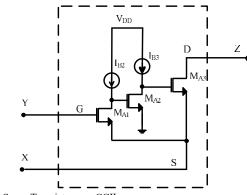

For typical parameter values;  $r_s$ ,  $A_v$  and  $r_d$  are in  $\Omega$ , unity and  $G\Omega$  ranges, respectively. These interesting features lead us to consider a single super transistor as a high performance CCII as is shown in Fig. 3 which has very low impedance at X terminal, close to unity gain between Y and X terminals and very high output impedance at Z terminal. Despite the intrinsic capacity of STs to operate as a CCII, up to now, they have not been employed in the structure of current conveyors. Here for the first time, we employ ST as the core part of a high performance CCII.

Fig 3. Super Transistor as a CCII.

As it is seen from Fig. 3, there is a DC level shift equal to  $V_{GSMA1}$  between Y and X terminals. Transistor  $M_{A3}$  also requires DC bias current. Therefore, some modifications in Fig. 3 are needed to make it a high performance CCII. Fig. 4 shows the simplified schematic of the proposed CCII which is made up of only 8 NMOS transistors (excluding bias circuitry). Transistor  $M_1$  which is identical to  $M_{A1}$  is used to reduce DC offset voltage between Y and X terminals. For DC input, a simple analysis shows that gate voltage of  $M_1$  and  $V_X$  can be expressed as:

$$V_{G_{M1}} = V_{Y} + V_{GS_{M1}},$$

(5)

$$V_{X} = V_{G_{M1}} - V_{GS_{MA1}} = V_{Y} + V_{GS_{M1}} - V_{GS_{MA1}}.$$

(6)

Therefore, for  $V_{Y} = 0$ , offset voltage can be found as

$$V_{off} = V_X - V_Y = V_X = V_{GS_{M1}} - V_{GS_{MA1}},$$

(7)

which can be expressed as (Appendix-A)

$$V_{\rm off} \approx \frac{K \times \lambda}{2} (V_{\rm DSMA1} - V_{\rm DSM1}). \tag{8}$$

Evidently, low offset voltage can be achieved by making  $V_{DSMA1}$  as close as possible to  $V_{DSM1}$ .

In Fig. 4 current sources  $I_{B2}$  and  $I_{B3}$  should be equal to provide matching between  $M_1$  and  $M_{A1}$ . In addition, current sources  $I_{B1}$  and  $I_{B2}$  should also be equal because any difference between  $I_{B1}$  and  $I_{B2}$  will appear as an offset current at Y terminal.

Fig. 4. Simplified schematic of the proposed CCII.

By performing a simple small-signal analysis and using (3), voltage transfer between Y and X terminals can be expressed as (Appendix-B)

$$\frac{\mathbf{v}_{\mathbf{X}}}{\mathbf{v}_{\mathbf{Y}}} \approx \frac{\mathbf{g}_{\mathrm{m1}}\mathbf{r}_{\mathrm{oIB2}}}{1 + \mathbf{g}_{\mathrm{m1}}\mathbf{r}_{\mathrm{oIB2}}} \approx 1, \tag{9}$$

where  $g_{mi}$  and  $r_{oIBi}$  are transconductance and output resistance of related transistor and current source, respectively.

If we neglect the effect of negative feedback established by  $M_2$ - $M_5$  and only consider the effect of super transistor, the impedance at X terminal can be expressed as (2) (by replacing  $r_{oIB2}$  and  $r_{oIB3}$  with  $r_{oIB3}$  and  $r_{oIB4}$ , respectively). However, if a single transistor ( $g_{mA1}$ ) is used instead of super-transistor, the impedance at X terminal will be

$$\mathbf{r'}_{\mathbf{x}} \approx \frac{1}{g_{\mathsf{mA1}}}.$$

(10)

Considering (9) and comparing (2) and (10), shows that innovative use of super transistor not only increases the voltage transfer accuracy between X and Y terminals, but it results in a significant reduction in X terminal impedance.

Cascode current mirror formed by transistors  $M_2$ – $M_5$  serves three vital functions:

First; it duplicates the current in the X terminal to the Z output (assuming that  $I_{B3} + I_{B5} = I_{B6}$ ).

Second; it provides high impedance at Z terminal.

Third; it forms a negative feedback loop that further reduces the impedance at X terminal.

As it can be seen, several important features are provided by only 4 transistors resulting in low power consumption, compact and easy to design structure.

By considering the effect of negative feedback formed by  $M_2-M_5$  transistors and using (2), the overall impedance at X terminal is found as:

$$r'_{x} \approx \frac{(1 + g_{m2}g_{m4}^{-1})}{g_{mA1}g_{mA2}g_{mA3}(r_{0A1} \| r_{0IB3})(r_{0A2} \| r_{0IB4})r_{0IB5}g_{m2}}.$$

(11)

From (11), it is evident that the proposed CCII enjoys very low impedance at X terminal.

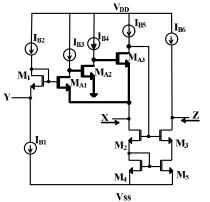

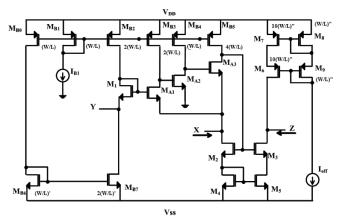

Complete schematic of the proposed CCII is shown in Fig. 5 in which ideal current sources are implemented by simple current mirrors made of transistors  $M_{B0}-M_{B7}$ . Besides, transistors  $M_6-M_9$  and current source  $I_{off}$  are used to provide DC current for  $M_2-M_5$  transistors. Cascode structures made of transistors  $M_2-M_5$  and  $M_6-M_9$  at the output branch are used to increase impedance at Z terminal. Analysing circuit of Fig. 5, the impedance at Z terminal is found as

$$R_{Z} \cong (g_{m3}r_{o3}r_{o5}) \| (g_{m6}r_{o6}r_{o7}).$$

(12)

The impedance at Y terminal is also found as

$$R_{Y} \cong r_{oB7} \| (g_{m1}^{-1} + r_{oIB2}).$$

(13)

As it is seen from (13), the impedance at Y terminal is not infinite. Limited impedance at Y terminal can only cause a negligible reduction in  $\beta$  value of CCII. By considering R<sub>Y</sub>, the amount of reduction will be

$$K = \frac{RY}{RY + RS},\tag{14}$$

where  $R_S$  is the internal impedance of voltage source connected to Y terminal. As  $R_S$  is in ohm range, and  $R_Y$  is in kohm range, therefore,  $K \approx 1$  and the limited impedance will not have a serious effect on CCII's performance. However, if larger impedances at Y terminal is required, simple current mirrors used for biasing, can be replaced with high output impedance cascode type current mirrors.

Fig. 5. Complete schematic of the proposed CCII.

# B. Simulation Results

Performance of the proposed circuit of Fig. 5 is verified by HSPICE simulations using 0.18  $\mu$ m TSMC CMOS process parameters under supply voltage of ±0.9 V. Transistors aspect ratios are reported in TABLE I. According to the transistors aspect ratios shown in Fig. 5, to satisfy I<sub>Z</sub> = I<sub>X</sub> we should have 10 × I<sub>off</sub> = 6 × I<sub>B1</sub>. The values of I<sub>B1</sub> and I<sub>off</sub> are set at 15  $\mu$ A and 9  $\mu$ A respectively. A compensation capacitor of 0.4 pF is also added between gate and drain of M<sub>A3</sub> for frequency compensation. DC transfer characteristic of X terminal voltage (V<sub>X</sub>) against input voltage at terminal Y (V<sub>Y</sub>) (shown in Fig. 6) is achieved while Z terminal is connected to ground. Figure 6(a) shows that maximum and minimum voltage limits at terminal X are 350 mV and -350 mV, respectively. Figure 6(b) shows that DC offset voltage at X terminal for V<sub>Y</sub>=0 is also negligible value of 5.6  $\mu$ V.

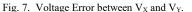

Figure 7 shows error voltage between X and Y terminals for different values of  $V_Y$ . Favourably, error voltage between X and Y voltage remains below 25 mV. In Fig. 8 an input sinusoidal voltage having amplitude of 100 mV and frequency of 100 kHz, is applied to Y node, and the resulting signal on X-terminal is observed. THD is only 0.31 %. By increasing frequency, the value of THD reaches to 0.23 % and 0.21 % at 1 MHz and 10 MHz, respectively.

| TABLE I. TRANSIST | TORS ASPECT RAT | IOS. |

|-------------------|-----------------|------|

|                   |                 |      |

| Transistors                       | W(µm) | L(µm) |  |  |

|-----------------------------------|-------|-------|--|--|

| $M_{B0}, M_1, M_{A1}, M_{B4}$     | 18    | 0.27  |  |  |

| $M_{A3}, M_{B1}$                  | 18    | 0.27  |  |  |

| M <sub>B2</sub> , M <sub>B3</sub> | 36    | 0.27  |  |  |

| M <sub>A2</sub>                   | 9     | 0.27  |  |  |

| M <sub>B5</sub>                   | 72    | 0.27  |  |  |

| M <sub>B6</sub>                   | 1.8   | 0.27  |  |  |

| M <sub>2</sub> , M <sub>3</sub>   | 9     | 0.36  |  |  |

| M4, M5                            | 5.4   | 0.54  |  |  |

| $M_{6}, M_{7}$                    | 36    | 0.36  |  |  |

| M <sub>8</sub> , M <sub>9</sub>   | 3.6   | 0.36  |  |  |

| M <sub>B7</sub>                   | 3.6   | 0.27  |  |  |

Fig. 6.  $V_X$  versus  $V_Y$  changing from a) -0.9 V to +0.9 V b) around 0 V.

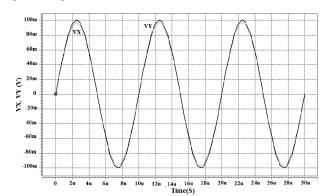

The change in the Z terminal output current against the X terminal input current is also shown in Fig. 9 in which  $I_X$  is changed from -85  $\mu$ A to +85  $\mu$ A. Favourably, the input impedance at X terminal is 0.155  $\Omega$  which is very close to the ideal value of zero. Such low input impedance at X terminal is a direct result of using super transistor according

to (11). The impedance at Z and Y terminals are 1.6 M $\Omega$  and 47 k $\Omega$ , respectively. Total power dissipation is also 0.451 mW.

Fig. 8.  $V_X$  and  $V_Y$  in time domain.

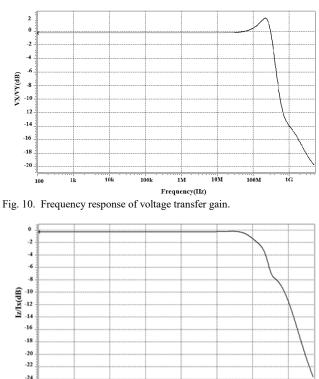

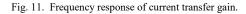

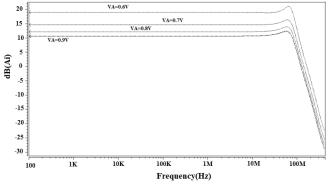

The frequency response of  $(V_X/V_Y)$  is shown in Fig. 10 where, V<sub>Y</sub> is the AC signal, X terminal is open circuited and Z terminal is grounded. The proposed CCII has a wide voltage gain -3 dB bandwidth of 377 MHz with a gain of 0.969. As it is seen, the voltage transfer response shows a peak of 2 dB. If a flat response is required, the value of compensation capacitor should be increased to 1 pF, however it will result in degradation in frequency performance. Figure 11 shows the frequency response of Iz versus I<sub>X</sub> where, Y and Z terminals are connected to ground and AC current signal is applied to X terminal. The proposed CCII exhibits a current gain -3 dB bandwidth of 195 MHz and current transfer gain of 0.965. The resulted high frequency performance is due to the fact that only NMOS transistors are used in processing voltage and current signals. In addition, they are all included in negative feedback loop which further improves frequency performance.

16

100M

1001

1M

Frequency(Hz)

103

ik

Overall characteristic of the proposed CCII is compared with previously reported works in Table II. As it is seen, although CCII of [3] exhibits impedance of less than 7  $\Omega$  at X terminal, but it suffers from low voltage and current bandwidths of 10.5 MHz and 6.2 MHz, respectively. The CCII of [4] enjoys high voltage and current bandwidths but it exhibits low impedance of 147  $k\Omega$  at Z terminal and consumes 1.3 mW. The low power CCII of [12] exhibits wide voltage bandwidth of 10 GHz, but its current bandwidth is only 32 MHz. The CCII of [15], exhibits moderate frequency performance, consumes high power consumption and exhibits high impedance of 47  $\Omega$  at X terminal. The CCII of [18] also exhibits Rx value of 11.4  $\Omega$ , poor frequency performance of 16 MHz and requires high supply voltage of  $\pm 1.5$  V. The proposed CCII exhibits very low impedance at X terminal which is at least 45 times smaller than that of [3], [4], [12], [15], [18], [22], [23]. Its offset voltage at X terminal is only 5.6  $\mu$ V which is the smallest one in Table II. Its output impedance is 1.6 M $\Omega$  and comparable to [15] but much larger than [4]. The output impedance is high enough to enable easy cascading, however it can further be improved by utilizing another ST at output branch. The proposed CCII's power consumption is two times larger than those of [3], [12], [18] but much smaller than [4], [15]. Compared to [22], [23], the proposed CCII has better frequency performance and lower input (X terminal) impedance. As it is seen in Table II, the proposed CCII has not very high impedance at Y terminal but as it will be shown, this property will not cause any problem in most of the applications.

# **III. APPLICATIONS OF THE PROPOSED CCII**

In this section, applications of the proposed CCII as an instrumentation amplifier, a variable-gain voltage amplifier and a variable gain current amplifier are given. In all of these applications the advantage of using high performance CCII is obvious.

## A. Instrumentation Amplifier

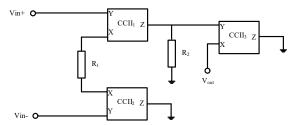

Figure 12 shows the application of the proposed CCII to implement instrumentation amplifier of [9]. If both CCIIs are well matched and have precise voltage tracking between their Y and X terminals, high common-mode rejection ratio (CMRR) is provided. Unlike conventional voltage-mode instrumentation amplifiers, this circuit does not rely on any external resistor matching to achieve high CMRR, however ultimate limit on CMRR is determined by the mismatch between CCII<sub>1</sub> and CCII<sub>2</sub>. The differential-mode voltage gain and output impedance can be described as:

$$V_{out} = \left(\frac{R_{Y_1}}{R_{Y_1} + R_S}\beta_1 V_{in+} - \frac{R_{Y_2}}{R_{Y_2} + R_S}\beta_2 V_{in-}\right)\alpha_1\beta_3 \frac{R_2 \|R_{Y_3}}{R_1 + R_{x_1} + R_{x_2}},(15)$$

$$R_{out} = R_{x_3}, \qquad (16)$$

where  $R_{x3}$  is the x-terminal impedance of CCII<sub>3</sub>,  $R_{Y1}$ ,  $R_{Y2}$ and R<sub>Y3</sub> are impedances at Y terminal of CCII<sub>1</sub>, CCII<sub>2</sub> and CCII<sub>3</sub>, respectively, and  $R_{S1}$  and  $R_{S2}$  are the internal impedances of voltage sources Vin+ and Vin-, respectively. As  $R_{Y3} >> R_2$ ,  $R_{Y1} >> R_{S1}$ ,  $R_{Y2} >> R_{S2}$ ,  $R_{x1}$  and  $R_{x2} << R_1$ , and  $\alpha, \beta \approx 1, (15)$  can be expressed as

$$\frac{V_{out}}{V_{in+}-V_{in-}} \cong \frac{R_2}{R_1}.$$

(17)

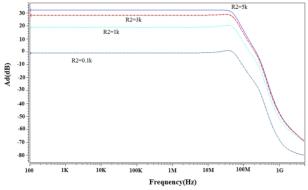

In order to verify the performance of the instrumentation amplifier of Fig. 12,  $R_1$  is set to 0.1 k $\Omega$ , while  $R_2$  is varied from 0.1 k $\Omega$  to 5 k $\Omega$ . Figure 13 shows that while DC differential gain varies from 0 dB to 33 dB, -3 dB bandwidth varies only from 67 MHz (for gain of 0 dB) to 53 MHz (for gain of 33 dB). The -3 dB bandwidth proves to be approximately constant at high frequency for different gain values.

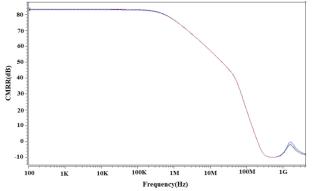

CMRR frequency performance is also shown in Fig. 14. As it can be seen, the instrumentation amplifier of Fig. 12 exhibits CMRR of 83 dB with -3 dB bandwidth of 613 kHz for different values of R<sub>2</sub>.

Fig. 12. Application of the proposed CCII as instrumentation amplifier [9].

For instrumentation amplifier application, using the proposed CCII results in three major improvements:

1. High CMRR because of the proposed CCII's high accuracy in transferring input signals from Y terminal to X terminal which is achieved because of the used super transistor.

2. Very low output impedance of 0.155  $\Omega$  because of very low impedance at X terminal which is achieved because of the used super transistor and negative feedback loop.

3. High frequency performance due to the high frequency performance of the proposed CCII.

| Parameters                       | [3]        | [4]            | [12]*           | [15]   | [18]        | [21]  | [22]  | Proposed |

|----------------------------------|------------|----------------|-----------------|--------|-------------|-------|-------|----------|

| Rx(Ω)                            | <7         | 9.6            | 15              | 42     | 11.4        | 200   | 27    | 0.155    |

| Rz (MΩ)                          | NA         | 0.147          | NA              | 2.24   | 7.2         | 0.560 | 0.89  | 1.6      |

| RY                               | 00         | œ              | 8               | 147 kΩ | x           | œ     | œ     | 47 kΩ    |

| Vx/Vy BW(MHz)                    | 10.5       | 810            | 10000           | 87     | 16          | 99    | 14    | 377      |

| Iz/Iy BW(MHz)                    | 6.2        | 915            | 32              | 70     | NA          | 94    | 13    | 195      |

| Offset voltage at X(mV)          | <2.5       | 0.8            | NA              | 0.2    | NA          | NA    | NA    | 0.0056   |

| PD(mW)                           | 0.213      | 1.3            | 0.234           | 2.24   | 0.210       | 1.5   | 0.064 | 0.451    |

| Technology (µm)                  | 0.35       | 0.35           | 0.5             | 0.8    | 0.35        | 0.13  | 0.18  | 0.18     |

| Input Voltage dynamic range (mV) | $\pm 650$  | (-1.43)-(+1.1) | (-0.63)-(+0.34) | NA     | (-1)-(+0.9) | 1.5   | ±380  | ±350     |

| Input current dynamic range (µA) | $\pm 1000$ | ±3000          | ±100            | NA     | NA**        | NA    | ±7    | ±80      |

| No. of transistors               | 22         | 20             | 14              | 28     | 21          | 25    | 36    | 21       |

| Supply Voltage (V)               | ±0.75      | ±1.65          | ±1.5            | 3.3    | ±1.5        | 1.5   | ±0.4  | ±0.9     |

TABLE II. COMPARISON BETWEEN PROPOSED CCII AND OTHER RECENT WORKS.

Note: \*low power wide band version, \*\* Not Available.

Fig. 13. Frequency response of Differential-Gain of Fig. 12 for  $R_1$  = 0.1  $k\Omega$  and different values of  $R_2.$

Fig. 14. Frequency response of CMRR for  $R_1$  = 0.1  $k\Omega$  and different values of  $R_2.$

# B. Variable Gain Voltage Amplifier

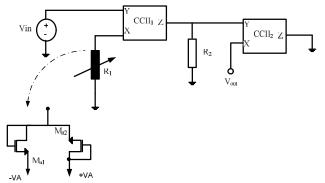

Figure 15 shows a variable-gain voltage amplifier implemented by the proposed CCII. The input voltage applied to  $Y_1$  terminal is transferred to  $X_1$  terminal, where it is translated to current by  $R_1$ . The output voltage and output impedance can be simply derived as:

$$A_{v} = \frac{V_{out}}{V_{in}} = \frac{R_{Y1}}{R_{Y1} + R_{S}} \beta_{1} \propto_{1} \beta_{2} \frac{R_{2} \| R_{Y2}}{R_{1}} \approx \frac{R_{2}}{R_{1}}, \quad (18)$$

$$R_{out} = R_{x2}, \tag{19}$$

where  $R_{x2}$  is the X terminal impedance of CCII<sub>2</sub>. To have electronic control, a variable resistor [17] is used as  $R_1$ . Therefore, the value of voltage gain can be set by control voltages  $V_A$  and  $-V_A$  resulting in a high-performance electronically tunable voltage amplifier.

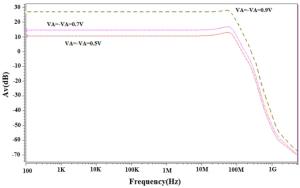

Figure 16 shows the frequency performance of the proposed voltage amplifier. As it can be seen from Fig. 16,

-3 dB bandwidth of the proposed voltage amplifier varies between 97 MHz to 85 MHz for different voltage gains from 10 dB to 28 dB respectively. It also exhibits very low output impedance of only 0.155  $\Omega$ .

Fig. 15. Application of the proposed CCII as a high-performance variablegain wide-bandwidth voltage amplifier.

Fig. 16. Gain frequency response of the voltage amplifier of Fig. 15.

Using the proposed CCII in voltage amplifier application results in two major improvements:

1. Low output impedance equal to the X terminal impedance of the proposed CCII.

2. Very wide bandwidth as a result of the proposed CCII's high-frequency performance.

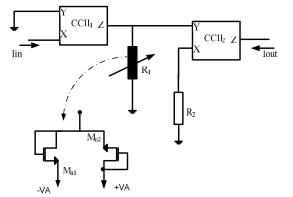

## C. Variable Gain Current Amplifier

A CCII based variable-gain current amplifier is shown in Fig. 17. In current amplifier of Fig. 17, the input current applied to the low impedance  $X_1$  terminal is transferred to the  $Z_1$  terminal, where it is translated to voltage by  $R_1$ . The voltage produced at  $Z_1$  terminal is copied to the  $X_2$  terminal where it is converted again to current by  $R_2$ . The current

produced at  $R_2$  is copied to output terminal ( $Z_2$ ). The current gain, output and input impedances can be simply derived as:

$$A_{i} = \frac{i_{out}}{i_{in}} = \alpha_{1} \ \beta_{2} \ \alpha_{2} \ \frac{R_{1} \| R_{Y2}}{R_{2} + R_{Y2}} \approx \frac{R_{1}}{R_{2}}, \tag{18}$$

$$R_{out} = R_{z2}, \qquad (19)$$

$$\mathbf{R}_{\mathrm{in}} = \mathbf{R}_{\mathrm{x1}},\tag{20}$$

where  $R_{z2}$  is the Z terminal impedance of CCII<sub>2</sub>. A variable resistor [17] is used as  $R_1$  to provide electronic tuning capability for the proposed CCII-based current amplifier. In Fig. 17, current gain can be tuned by control voltages  $V_A$ and  $-V_A$ .

Fig. 17. Application of the proposed CCII as a high-performance variablegain wide bandwidth current amplifier.

Figure 18 shows the frequency performance of the current amplifier of Fig. 17. Interestingly, for  $R_2 = 100 \Omega$  and different values of  $V_A$ , -3 dB bandwidth of the proposed current amplifier varies between 81.1 MHz to 90 MHz for different current gains ranging from 10.6 dB to 19 dB, respectively. The input and output impedances are also 0.155  $\Omega$  and 1.6 M $\Omega$  respectively.

Fig. 18. Gain frequency performance of the current amplifier of Fig. 17.

Using the proposed CCII in current amplifier application results in two major improvements:

1. Low input impedance equal to the X terminal impedance of the proposed CCII and high output impedance equal to Z terminal impedance of the proposed CCII.

2. Very wide bandwidth as a result of the proposed CCII's high frequency performance.

# IV. CONCLUSIONS

A new super transistor-based CCII for low-voltage high frequency applications, has been designed. The proposed CCII can operate at low supply voltage and exhibits very low impedance at its X terminal. It also exhibits wide frequency performance for both voltage and current transferring. As other merit, the proposed topology exhibits an extremely low offset voltage at X node, therefore, the need for any offset voltage cancellation circuit is alleviated resulting in a very simple structure. The performance of the proposed CCII in applications such as instrumentation amplifier, variable-gain voltage amplifier and variable-gain current amplifier has been tested. The achieved results prove that the proposed CCII is highly suitable for wideband lowvoltage low-power applications.

# REFERENCES

- A. S. Sedra, K. C. Smith, "A second-generation current-conveyor and its applications", *IEEE Trans. Circuit Theory*, vol. 17, no. 1, pp. 132– 134, 1970. DOI: 10.1109/TCT. 1970.1083067.

- [2] L. Safari, J. Azhari, "A novel wide band super transistor based voltage feedback current amplifier", *International Journal of Electronics and Communications*, vol. 67, no. 7, pp. 624–631, 2013. DOI: 10.1016/j.aeue.2013.01.005.

- [3] A. H. Madian, M. Soliman, A. M. Soliman, "New 1.5-V CMOS second generation current conveyor based on wide range transconductor", *Analog Integrated Circuits and Signal Processing*, vol. 49, pp. 267–279, 2006. DOI: 10.1007/s10470-006-9703-3.

- [4] E. Arslan, S. Minaei, A. Morgul, "On the realization of high performance current conveyors and their applications", *Journal of Circuits, Systems and Computers*, vol. 22, 2013. DOI: 10.1142/S0218126613500151.

- [5] K. Gosh, B. N. Ray, "CCII based nth order current mode filter with grounded R and C", *International Journal of Electronics Letters*, vol. 3, pp. 105–121, 2013. DOI: 10.1080/21681724.2014.911366.

- [6] T. Ettaghzouti, N. Hassan, K. Besbes, "Transformation of voltage mode filter circuit based on op-amp circuit based on CCII", *Journal of Electronic Science and Technology*, vol. 13, pp. 60–67, 2015.

- [7] E. Yuce, S. Minaei, "New CCII-based versatile structure for realizing PID controller and instrumentation amplifier", *Microelectronics Journal*, vol. 41, pp. 311–316, 2010. DOI: 10.1016/j.mejo.2010.03. 008.

- [8] A. A. Khan, M. A. Al-Turaigi, M. A. El-Ela, "An improved currentmode instrumentation amplifier with bandwidth independent of gain", *IEEE Trans. Instrumentation Measurement*, vol. 44, no. 4, pp. 887– 891, 1995. DOI: 10.1109/19.392876.

- [9] C. Toumazou, F. G. Lidgey, "Novel current mode instrumentation amplifier", *Electronics Letters*, vol. 25, no. 3, pp. 228–230, 1989. DOI: 10.1049/el:19890163.

- [10] T. Kaulberg, "A CMOS current-mode operational amplifier", Eighteenth European Solid-State Circuits Conference (ESSCIRC 1992), 1992. DOI: 10.1109/ESSCIRC. 1992.5468207.

- [11] A. M. Soliman, "Current Mode Oscillators using single output current conveyors", *Microelectronics Journal*, vol. 29, no. 11, pp. 907–912, 1998. DOI: 10.1016/S0026-2692(98)00053-6.

- [12] W. S. Hassanein, I. A. Awad, A. M. Soliman, "New wide band low power CMOS current conveyors", *Analog Integrated Circuits and Signal Processing*, vol. 40, no. 1, pp. 91–97, 2004. DOI: 10.1023/B:ALOG.0000031439.62496.f9.

- [13] L. Grigorescu, "Amplifiers built with current-conveyors", Journal of Applied Physics-Instruments, vol. 53, pp. 109–113, 2008.

- [14] S. S. Rajput, S. S. Jamuar, "Low voltage low power and high performance current conveyors for low voltage analog and mixed mode signal processing applications", *Analog integrated Circuits and Signal Processing*, vol. 41, no. 1, pp. 21–34, 2004. DOI: 10.1023/B:ALOG.0000038280.45676.e0.

- [15] B. Calvo, S. Celma, P. A. Martinez, M. T. Sanz, "High-speed highprecision CMOS current conveyor", *Analog Integrated Circuits and Signal Processing*, vol. 36, no. 3, pp. 235–238, 2003. DOI: 10.1023/A:1024770405352.

- [16] A. Naik, N. M. Devashrayee, "Two novel long-tail pair based second generation current conveyors (CCII)", *Information Technology and Mobile Communication*, vol. 147, pp. 95–99, 2011. DOI: 0.1007/978-3-642-20573-6\_15.

- [17] L. Safari, S. Minaei, E. Yuce, "A new transresistance mode instrumentation amplifier with low number of MOS transistors and Electronic tuning opportunity", *Journal of Circuits systems and*

computers, vol. 25, no. 4, 2016. DOI: 10.1142/S0218126616500225.

- [18] G. Ferri, V. Stornelli, M. Fragnoli, "An integrated improved CCII topology for resistive sensor application", *Analog Integrated Circuits* and Signal Processing, vol. 48, pp. 247–250, 2006. DOI: 10.1007/s10470-006-7415-3.

- [19] A. Fabre, O. Saaid, H. Barthelemy, "On the frequency limitations of the circuits based on second generation current conveyors", *Analog Integrated Circuits and Signal Processing*, vol. 7, pp. 113–129, 1995. DOI: 10.1007/BF01239166.

- [20] H. Jia, Y. L, "Design of a novel wideband op amp with CCII structure", *Analog Integrated Circuits and Signal Processing*, vol. 85, pp. 445–449, 2015. DOI: 10.1007/s10470-015-0611-2.

- [21] X. Zhao, H. Fang, J. Xu, "DC gain Enhancement method for recycling folded cascode amplifiers in deep submicron technology", *IEICE Electronics Express*, vol. 8, no. 17, pp. 1450–1454, 2011. DOI: 10.1587/elex.8.1450.

- [22] A. Redan, M. Ibrahim, F. Farag, "Input-output Rail-to-Rail CMOS CCII for low voltage-low power applications", *Microelectronics Journal*, vol. 48, pp. 60–75, 2016. DOI: 10.1016/j.mejo.2015.12.001.

- [23] M. Kumngern, F. Khateb, "0.5-VBulk-driven second generation current conveyor", in Proc. IEEE Symposium on Computer Applications and Industrial Electronics (ISCAIE 2014), Penang, Malaysia, 2014, pp. 1–2. DOI: 10.1109/ISCAIE.2014.7010233.

- [24] J. M. Martinez-Heredia, A. Torralba, "Enhanced source-degenerated CMOS differential transconductor", *Microelectronics Journal*, vol. 42, no. 2, pp. 396–402, 2011. DOI: 10.1016/j.mejo.2010.10.011.

### APPENDIX A

For V<sub>GSM1</sub> and V<sub>GSMA1</sub> we have:

$$\begin{split} V_{GSM1} &= \left| \frac{I_{B2}}{\frac{1}{2} \mu_n C_{ox} \left( \frac{W}{L} \right)_{M1} (1 + \lambda V_{DSM1})} + V_{thM1} \approx \right. \\ &\approx K_1 \left( 1 - \frac{\lambda V_{DSM1}}{2} \right) + V_{thM1}, \end{split} \tag{A.1}$$

In which:

$$K_1 = \sqrt{\frac{I_{B2}}{\frac{1}{2}\mu n Cox(\frac{W}{L})_{M1}}},$$

(A.3)

(A.2)

$$K_{2} = \sqrt{\frac{I_{B3}}{\frac{1}{2}\mu n Cox(\frac{W}{L})_{MA1}}}.$$

(A.4)

For  $K_1 = K_2 = K$  and  $V_{thM1} = V_{thMA1}$  (assuming identical transistors), by inserting (A.1) and (A.2) into (7), offset voltage is found as

$\approx \mathrm{K}_{2} \left(1 - \frac{\lambda \mathrm{V}_{\mathrm{DSMA1}}}{2}\right) + \mathrm{V}_{\mathrm{thMA1}}.$

$$V_{\text{off}} \approx \frac{\kappa \lambda}{2} (V_{\text{DSMA1}} - V_{\text{DSM1}}). \tag{A.5}$$

### APPENDIX B

$$\times \frac{\frac{V_{X}}{V_{Y}} = \frac{g_{m1}r_{oIB2}}{1 + g_{m1}r_{oIB2}} \times \frac{1}{1 + [g_{mA1}(r_{oA1}||r_{oIB3})g_{mA2}(r_{oA2}||r_{oIB4})]^{-1}} \approx \frac{g_{m1}r_{oIB2}}{\approx \frac{g_{m1}r_{oIB2}}{1 + g_{m1}r_{oIB2}}} \approx 1,$$

(B.1)

where  $g_{mi}$  and  $r_{oIBi}$  are transconductance and output resistance of related transistor and current source, respectively.