# Design and Applications of Electronically Tunable Floating Resistor Using Differential Amplifier

S. A. Tekin<sup>1</sup>, M. Alçı<sup>1</sup>

<sup>1</sup>Department of Electrical and Electronics Engineering, Erciyes University, 38039, Kayseri, Turkey satekin@erciyes.edu.tr

Abstract—In this paper, a new electronically tunable active resistance was introduced. The proposed circuit design consists of only two differential amplifiers. The main advantages of this circuit are higher bandwidth, simpler design and tunable resistance range. Also, the design of the circuit allows negative resistance structure and besides it can be used in IC realizations. Effective range of the floating resistor is controlled within a wide range of resistance in between  $\pm$  43  $\Omega$  –  $\pm$  516 k $\Omega$ .

*Index Terms*—Active resistor, current amplifier, current mode circuits, differential amplifier.

# I. INTRODUCTION

The floating and grounded resistors in technology of silicon can be realized by using diffusion areas or polysilicon in an integrated circuit. Nevertheless, large areas of silicon chip are required to obtain these resistors. This technique is inconvenient to attain certain values. Also, it is not possible to tune the targeted values of resistance. So MOS and bipolar based active resistors have been introduced in previous studies to overcome these limitations [1].

The diverse analogue circuits, for example, filters, oscillators and amplifiers, are necessary for high performance electronically controllable active resistors. [2]–[5]. Several CMOS circuits simulating controlled resistors have been proposed in the literature [6]–[8]. Electronically tunable resistors which process in MOS technologies have been introduced. However, these resistors are not able to operate at high frequencies [9], [10]. In addition, the only voltage signal is used to drive these circuits. Thus, the ability of these circuits is limited and these circuits exhibit severe frequency limitations, essentially when low values of the simulated resistances are needed. This is due to the gatedrain and gate-source parasitic capacitances of the MOS transistors [11]. Also, the tuning ranges of the resistor which designed in MOS transistors are narrow [6], [12].

Some circuit applications used in general impedance converters (GICs) have the significant advantages of the achieving resistors by easily changing the feedback connections in the circuits. Passive components are usually used for designing GIC circuits. However, using passive device is not proper and impractical for integrated circuit implementations [13], [14].

A bipolar based floating controlled resistance has also been described in the literature [15], [16]. Also, it is introduced voltage controlled floating resistor using OTA in previous study [17]. But these studies suffer from narrow bandwidth and circuit complexity. Bipolar based current-controlled resistance is proposed in this paper as a way to avoid these problems.

Recently, some differential amplifier based circuits have been proposed in the literature [18]–[20]. It is introduced a floating resistance based on a pair of differential amplifier has the ability to operate at high frequencies in this paper. This resistor, which merely contains bipolar transistors, is very convenient for IC implementation. More components are not utilized in the circuit with the aim of keeping the low circuit complexity and the simpler design.

In this article, first, theoretical analysis for a differential amplifier is explained. Thereafter, circuit analysis and simulation results of the tunable floating resistor design are demonstrated. Finally, the suitability of this floating resistor is indicated using oscillator and current amplifier.

### II. CIRCUIT DESCRIPTION

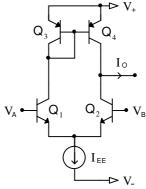

In this section, in order to carry out a simple circuit definition of the tunable active resistance as shown in Fig. 1, a basic differential amplifier is employed.

Fig. 1. Transconductance amplifier.

Manuscript received March 2, 2012; accepted November 25, 2012.

Transistors  $Q_1$  and  $Q_2$  convert input voltages to an output current as a transconductance amplifier.  $Q_3$  and  $Q_4$  act as a current mirror where  $I_{EE}$  is an input biasing current. Assuming that  $V_A$  and  $V_B$  are applied from base of transistors  $Q_1$  and  $Q_2$ , respectively, the difference between input voltages  $V_A$  and  $V_B$  of the transconductance amplifier is given by

$$V_A - V_B = V_{BE1} - V_{BE2} = V_T \left( \ln \frac{I_{C1}}{I_S} - \ln \frac{I_{C2}}{I_S} \right),$$

(1)

where  $V_{BE}$  is the junction voltage of the transistors. As shown in Fig. 1,  $I_{CI}$  and  $I_{C2}$  are the collector currents of the  $Q_1$  and  $Q_2$  transistors, respectively. Also,  $V_T$  is the thermal voltage and  $I_S$  is the reverse saturation current of the transistors.

In this case, collector currents can be written as following equations

$$\begin{cases} I_{EE} \cong I_{C1} + I_{C2}, \\ I_{C1} = \frac{I_{EE}}{\frac{-(V_A - V_B)}{V_T}}, \\ 1 + e^{\frac{-(V_A - V_B)}{V_T}}. \\ I_{C2} = \frac{I_{EE}}{\frac{V_A - V_B}{V_T}}. \end{cases}$$

(2)

The relation of  $I_0$  and input voltages of the transconductance amplifier can be expressed as

$$I_0 = I_{C1} - I_{C2} = I_{EE} \tanh\left(\frac{V_A - V_B}{2V_T}\right).$$

(3)

From (3), if  $V_A - V_B << 2V_T$  is assumed, then the function  $tanh[(V_A - V_B)/2V_T]$  is approximately equal to  $(V_A - V_B)/2V_T$ . The expression of this output current is

$$I_0 = I_{EE} \frac{V_A - V_B}{2V_T} \tag{4}$$

or

$$I_0 = G_m(V_A - V_B), (5)$$

where transconductance  $G_m = I_{EE}/2V_T$ . Considering the small signal analysis of transconductance amplifier, the output current can be given by

$$i_o = v_A \cdot \left(\frac{g_{m4} \cdot g_{m1}}{g_{m3}}\right) - v_B \cdot g_{m2}. \tag{6}$$

Since all transistors are operating at the same bias current,  $g_{m1} = g_{m2} = g_{m3} = g_{m4} = g_m$ , where

$$i_o = g_m(v_A - v_B). (7)$$

Thus, from (5) and (7) it can be seen that

$$G_m = g_m, (8)$$

which is identical to the result found for the amplifier pair.

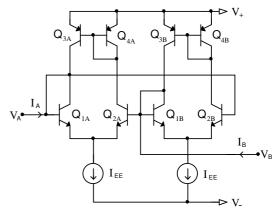

Fig. 2 shows schematic diagram for the proposed floating positive resistor. The proposed circuit consists of two matched amplifier pairs composed of  $Q_{1A}$  –  $Q_{2A}$  and  $Q_{1B}$  –  $Q_{2B}$ , respectively. The residual transistors are used as current mirrors. In order to inject copies of the biasing current into the transistors ( $Q_{3A}$  –  $Q_{4A}$ ) and ( $Q_{3B}$  –  $Q_{4B}$ ), these current mirrors are essential. The circuit is obtained by a parallel connection of the two transconductance amplifiers.

Fig. 2. Floating positive resistor.

Assuming that all the transistors are matched, an analysis of the circuit indicates that the currents  $I_A$  and  $I_B$  are written as

$$I_A = -I_B = G_m (V_A - V_B), \tag{9}$$

The resistance can now be found as

$$R_{AB} = \frac{V_A - V_B}{I_A} = \frac{2V_T}{I_{EF}} \,, \tag{10}$$

This means that the resistance value of the positive resistor will be tuned easily by bias current.

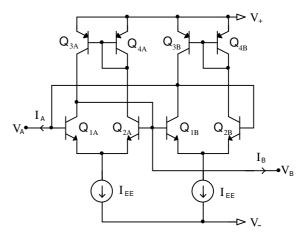

Fig. 3 shows the schematic diagram for the proposed floating negative resistor.

Fig. 3. Floating negative resistor.

The negative resistor structure is the same as positive resistor in terms of having components, but it is used different connections between components in the circuit as shown in Fig. 3.

Provided that all the transistors are matched, an analysis of the circuit which operates as a negative resistor indicates that the currents  $I_A$  and  $I_B$  are given by

$$I_B = -I_A = G_m (V_A - V_B).$$

(11)

The resistance can now be found as

$$R_{AB} = \frac{V_A - V_B}{-I_A} = -\frac{2V_T}{I_{EE}} \,. \tag{12}$$

This means that the negative resistance of the negative resistor will be tuned easily by bias current.

### III. PERFORMANCE ANALYSIS OF THE RESISTOR

### A. Mismatch of the areas

The mismatch effect of the transconductance amplifier shown in Fig. 1 is defined as an inequality in the base-emitter areas of the transistors  $Q_1$  and  $Q_2$ . Such a mismatch between transistors can be given as:

$$\begin{cases} I_{S1} = I_S + \frac{\Delta I_S}{2}, \\ I_{S2} = I_S - \frac{\Delta I_S}{2}. \end{cases}$$

(13)

Eq. (13) is defined as a proportional mismatch in the collector transport saturation current  $I_S$ . Thus, the bias current  $I_{EE}$  will be splitted between  $Q_1$  and  $Q_2$  transistors in proportion to their  $I_S$  values. When voltage  $V_A$  and  $V_B$  are grounded, collector currents of the transistors can be found as

$$\begin{cases} I_{C1} = \frac{I_0}{2} \left( 1 + \frac{\Delta I_S}{2I_S} \right), \\ I_{C2} = \frac{I_0}{2} \left( 1 - \frac{\Delta I_S}{2I_S} \right). \end{cases}$$

(14)

If the condition is  $V_A$  -  $V_B > 0$ , output current  $I_0$  will be as following equation

$$I_0 = g_m (V_A - V_B) + \left(\frac{I_{EE} \Delta I_S}{2I_S}\right).$$

(15)

For resistor, input current  $I_{AB}$  ( $I_{A}$ ) can be written as

$$I_{AB} = g_m (\mathbf{V_A} - \mathbf{V_B}) + \left(\frac{I_{EE} \Delta I_{SA}}{2I_{SA}}\right) - \left(\frac{I_{EE} \Delta I_{SB}}{2I_{SB}}\right), (16)$$

where  $I_{SA}$  is the collector transport saturation current of the  $Q_{1A}$  and  $Q_{2A}$ . Also  $I_{SB}$  is the collector transport saturation current of the  $Q_{1B}$  and  $Q_{2B}$ . From (16),  $R_{AB}$  is written as follows

$$R_{AB} = \frac{(V_{A} - V_{B})}{I_{AB}} = \frac{2V_{T}}{I_{EE}} + \frac{V_{T} (I_{SA} \Delta I_{SB} - I_{SB} \Delta I_{SA})}{I_{SA} I_{SB} I_{AB}}, \quad (17)$$

### B. Systematic output offset current

If  $V_A$  and  $V_B$  are grounded, the current-transfer ratio of a current mirror formed by transistors  $Q_3$  and  $Q_4$  in Fig. 1 can be found as

$$\frac{I_{C4}}{I_{C3}} = \frac{1}{1 + \frac{2}{\beta_p}},\tag{18}$$

where  $I_{C3}$  and  $I_{C4}$  are the collector currents of the transistors  $Q_3$  and  $Q_4$ , respectively. Also,  $\beta_p$  is the current gain of the PNP transistors in Fig. 1. Thus, the collector current of  $Q_4$  is given by

$$I_{C4} = \frac{I_{EE}}{2\left(1 + \frac{2}{\beta_p}\right)} \,. \tag{19}$$

Eq. (19) defines that output terminal has a current difference. The current difference  $\Delta i_o$  can be expressed as follows

$$\Delta i_0 = I_{C3} - I_{C4} = \frac{I_{EE}}{1 + \beta_p/2}.$$

(20)

If the condition is  $V_A$  -  $V_B > 0$ , output current  $I_0$  can be written

$$I_0 = g_m(V_A - V_B) - \frac{I_{EE}}{2\left(1 + \frac{2}{\beta_p}\right)}.$$

(21)

Improved current mirror such as MOS current mirror should be used to reduce offset current. Assuming perfect matching of the transistors in MOS current mirror, difference current  $\Delta i_o$  will always be zero. Thus, proposed resistor circuit can be used for BiCMOS applications.

## IV. SIMULATION RESULTS

The circuits in Fig. 2 and Fig. 3 were simulated using models for the transistors of the type NR100N and PR100N whose parameters are detailed in [21], in order to demonstrate the availability of the theory. The power supply is  $\pm$  1.5 V. The biasing current  $I_{EE}$  is changed between 0.1  $\mu$ A and 10 mA.

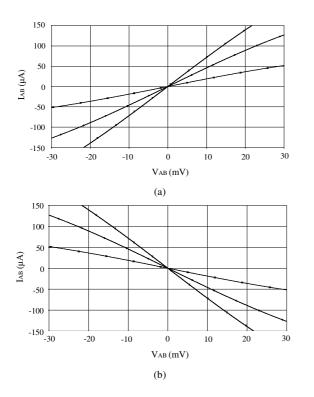

I-V characteristics of the positive resistor for different biasing current are shown in Fig. 4.

Fig. 4(a) depicts the I-V characteristics of the positive resistor for the diverse values of the  $I_{EE}$ . It is openly from the simulation results that the positive resistor can be exhibited reasonable good characteristics.

The I-V characteristics of the negative resistor for different biasing current are shown in Fig. 4(b). This figure displays, for the various values of the  $I_{EE}$ , the I-V

characteristics of the negative resistor. Although Fig. 2 and Fig. 3 have different connections, because of having similar structure, it is obvious that the negative resistor can be adjusted within reasonable values.

Fig. 4. I-V characteristics for: (a) positive resistor; (b) negative resistor.

Fig. 5 depicts the resistance  $R_{AB}$  at the resistor when  $I_{EE}$  is varied.

Fig. 5. Variation of the resistance with dc bias current for: (a) positive resistor; (b) negative resistor.

It is shown that the resistance value of the proposed resistor can be varied from  $\pm 5.16~\Omega$  to  $\pm 516~k\Omega$  with affinity between the theoretical and simulation results in Fig. 5 if bias current is tuned from 0.1  $\mu$ A to 10 mA. It is seen to be excellent linear behaviour when 0.1  $\mu$ A  $\leq I_{EE} \leq$  1.2 mA. The linear range of the resistor is  $\pm$  43  $\Omega$  –  $\pm$  516  $k\Omega$ .

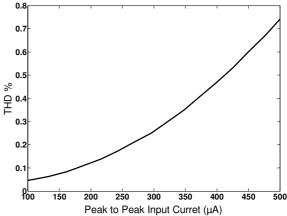

Fig. 6 depicts the changing percent total harmonic distortion (THD) versus peak to peak input current, for both the negative and positive resistor. THD %, which is a function of peak to peak magnitude of the input current, is calculated for  $R_{AB} = 258 \Omega$  and frequency = 1 MHz. It is shown that the THD % in the voltage across  $R_{AB}$  when the peak-to-peak magnitude of the input current  $I_{AB}$  is varied from 100 to 500  $\mu$ A, is found to change from 0.04 % to 0.747 %. It is clear that the THD is within reasonable values.

Fig. 6. THD % as a function of input current.

It is displayed the conclusions of the proposed floating resistor parameters in Table I.

TABLE I. PERFORMANCE PARAMETERS OF THE PROPOSED RESISTOR.

| Parameters                                      | Values                    |

|-------------------------------------------------|---------------------------|

| Power supply voltages                           | ±1.5V                     |

| Power consumption                               | 0.9 mW                    |

| -3dB Bandwidth                                  |                           |

| positive resistor $(V_{AB}/I_{AB})$             | 66.4 MHz                  |

| negative resistor $(V_{AB}/I_{AB})$             | 70.2 MHz                  |

| $R_{AB}$ ranges                                 | $43\Omega$ – $516k\Omega$ |

| The bias current range for controlling resistor | $0.1\mu A$ – $1.2  mA$    |

| THD (for $R_{AB}$ =258 $\Omega$ and 1Mhz)       | 0.747 %                   |

| References                                      | ±1.5V                     |

The -3dB bandwidths of positive resistor and negative resistor, respectively, are located at the 66.4 and 70.2MHz.

## V. APPLICATIONS OF THE PROPOSED RESISTOR

# A. Oscillator application

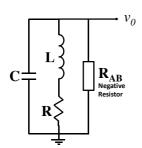

The application of the floating negative resistor is an oscillator, shown in Fig. 7 [1].

It consists of a floating negative resistor, a grounded capacitor and one inductor with loss. The negative resistor is necessary to set the oscillation condition of the circuit. Oscillator output waveform will still exist if the condition

$$\left| R_{AB} \right| \le \frac{\left( \omega_o L \right)^2}{R} \tag{22}$$

is met. This is known as the Barkhausen criterion for the oscillation.

Fig. 7. An oscillator used negative resistor.

The oscillation frequency of this oscillator can be expressed as

$$\omega_o = \frac{1}{\sqrt{LC}} \,. \tag{23}$$

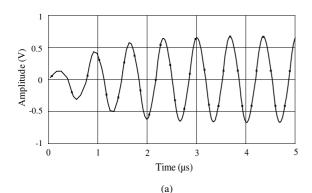

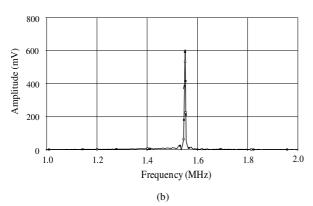

Fig. 8 shows the verified performance of the oscillator. In order to obtain the frequency responses of the oscillator, R, L and C are respectively, set to 250  $\Omega$ , 0.1 mH and 0.1 nF. Biasing current for negative resistor is 150  $\mu$ A.

Fig. 8. The simulation results of the voltage waveforms of the oscillator a) in time domain b) in frequency domain .

As shown in Fig. 8, the oscillation frequency of the circuit is 1.5503 MHz which well agrees with the calculated result.

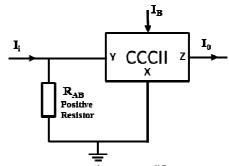

# B. Temperature compensated current amplifier

In literature, a temperature compensated scheme for a translinear current conveyor-based circuit was investigated [22]. This scheme has a disadvantage because it has complex circuit structure. Tunable current amplifier which has a simple structure for temperature compensation as an application of the positive resistor is shown in Fig 10. Current amplifier consists of the positive resistor and

controlled current conveyor (CCCII).

Fig. 9. Temperature compensated current amplifier.

The current  $I_0$  of the port Z is output current for CCCII. Additionally, port X of the CCCII is grounded and port Y constitutes the input of the circuit (Fig. 9).  $I_0$  is written as follow [23]

$$I_0 = 2I_B \frac{V_Y}{V_T},\tag{24}$$

where  $I_B$  is bias current of the CCCII. Also  $V_Y$  is the voltage of the port Y.  $V_Y$  can be written as

$$V_Y = R_{AB} . I_i = \frac{2V_T}{I_{EF}} I_i . \tag{25}$$

From (24) and (25), we can see that the current gain of the amplifier will be expressed as

$$A_{I} = \frac{I_{0}}{I_{i}} = 4 \frac{I_{B}}{I_{EE}}$$

(26)

In this instance, the current gain  $A_I$  of the circuit can be independent from thermal voltage  $(V_T)$ .

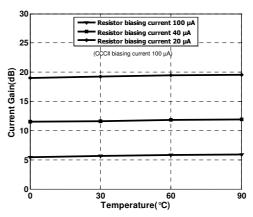

Fig. 10 depicts the changing current gain versus temperature for the temperature compensated current amplifier.

Fig. 10. The current gain of the amplifier for different biasing current of the positive resistor versus temperature.

It is clear that stable current gain is obtained at the different temperature values for the current amplifier. Also, the gain can be easily tuned by bias currents  $I_{EE}$  and  $I_B$ .

### VI. CONCLUSIONS

In this study, electronically tunable active resistor using

differential amplifier circuit was designed, and its applications to an oscillator and a current amplifier were tested. A basic differential pair is used to achieve a simple circuit implementation of the floating active resistor in this design. This circuit is used as either positive resistor or negative resistor by using different connection structures. The proposed resistors were simulated using a PSpice simulation program, and its simulation results were compared with the theoretical approaches. Theoretical analyses of these circuits were achieved, and the performance of the proposed resistors was verified by PSpice simulation results.

For proposed floating resistor, the resistance value can be tuned from  $\pm$  43  $\Omega$  to  $\pm$  516 k $\Omega$ , with perfect affinity between the theoretical and simulation results. From the frequency performance in Table 1, it can be seen that the -3 dB bandwidth is enhanced to 66.4 MHz and 70.2 MHz, respectively, for positive resistor and negative resistor. Finally, the adjustment capability of the introduced resistor is useful in electronic circuit designs and the circuit is rather convenient for bipolar and BiCMOS IC realizations.

## REFERENCES

- P. Pawarangkoon, W. Kiranon "Electronically tunable floating resistor", *International Journal of Electronics*, vol. 91, no. 11, pp. 665–673, 2004. [Online]. Available: http://dx.doi.org/10.1080/ 00207210412331330332

- [2] K. M. Al-Ruwaihi, "A floating voltage-controlled resistor and its application to active RC filter", *International Journal of Electronics*, vol. 82, no. 5, pp. 483–498, 1997. [Online]. Available: http://dx.doi.org/10.1080/002072197135869

- [3] R. Senani, V. K. Singh, "Synthesis of canonic single resistance controlled oscillator using a single current feedback amplifier", *IEE Proc. Circuits, Devices and Systems*, vol. 143, no. 1, pp. 71–72, 1996

- [4] S. Celma, P. A. Martinez, A. Carlosena, "Approach to the synthesis of canonic RC-active oscillator using CCII", *IEE Proc. Circuits*, *Devices and Systems*, vol. 141, no. 6, pp. 493–497, 1994.

- [5] H. Barthelemy, A. Fabre, "20-90 MHz current controlled sinusoidal oscillator", in *Proc. of the European Solid-State Circuits Conferences, Neuchatel, Switzerland*, 1996.

- [6] M. Gupta, R. Pandey, "FGMOS based voltage-controlled resistor and its applications", *Microelectronics Journal*, vol. 41, no. 6, pp. 25–32, 2010. [Online]. Available: http://dx.doi.org/10.1016/j.mejo. 2009.12.001

- [7] A. Manolescu, C. Popa, "Low-Voltage low-power improved linearity cmos active resistor circuits", *Analog Integrated Circuits and Signal Processing*, vol. 62, no. 3, pp. 373–387, 2010. [Online]. Available: http://dx.doi.org/10.1007/s10470-009-9351-5

- [8] A. Tajalli, Y. Leblebici, E. J. Brauer, "Implementing ultra-high-value floating tunable CMOS resistors", *Electronics Letters*, vol. 44, no. 5, pp. 349–350, 2008. [Online]. Available: http://dx.doi.org/ 10.1049/el:20082538

- [9] H. O. Elwan, S. A. Mahmoud, A. M. Soliman, "CMOS voltage controlled floating resistor", *International Journal of Electronics*, vol. 81, no. 5, pp. 571–476, 1996. [Online]. Available: http://dx.doi.org/10.1080/002072196136472

- [10] R. Senani, "Realization of linear voltage-controlled resistance in floating form", *Electronics Letters*, vol. 30, no. 23, pp. 1909–1910, 1994. [Online]. Available: http://dx.doi.org/10.1049/el:19941313

- [11] O. Saaid, A. Fabre, "Class AB current-controlled resistor for high performance current-mode applications", *Electronics Letters*, vol. 32, no. 1, pp. 4–5, 1996. [Online]. Available: http://dx.doi.org/ 10.1049/el:19960023

- [12] H. Zouaoui-Abouda, A. Fabre, "New high-value floating controlled resistor in CMOS technology", IEEE Transactions on Instrumentation and Measurement, vol. 55, no. 3, pp. 1017–1020, 2006. [Online]. Available: http://dx.doi.org/10.1109/ TIM.2006.873805

- [13] S. Al-Sarawi, "A novel topology for grounded-to-floating resistor conversion in CMOS technology", *Microelectronics Journal*, vol. 33, pp. 1059–1069, 2002. [Online]. Available: http://dx.doi.org/10.1016/ S0026-2692(02)00111-8

- [14] V. Riewruja, W. Petchmaneelumka, "Floating current-controlled resistance converters using OTAs", *International Journal of Electronics and Communications*, vol. 62, no. 10, pp. 725–731, 2008. [Online]. Available: http://dx.doi.org/10.1016/j.aeue. 2007.09.007

- [15] M. Barthelemy, A. Fabre, "A new floating controlled resistance operating in class AB", *IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications*, vol. 47. pp. 67–72, 2000. [Online]. Available: http://dx.doi.org/10.1109/81.817392

- [16] R. Senani, A. Singh, V. K. Singh, "A new floating current-controlled positive resistance using mixed translinear cells" *IEEE Transactions* on Circuits and Systems II, vol. 51. pp. 374–377, 2004. [Online]. Available: http://dx.doi.org/10.1109/TCSII.2004.831381

- [17] R. L. Geiger and E. Sánchez-Sinencio, "Active filter design using operational transconductance amplifiers: A Tutorial", *IEEE Circuits* and Devices Magazine, no. 1, pp. 20–32, 1985. [Online]. Available: http://dx.doi.org/10.1109/MCD.1985.6311946

- [18] M. Siripruchyanun, W. Jaikla, "Current controlled current conveyor transconductance amplifier (CCCCTA): a building block for analog signal processing", *Electrical Engineering (Archiv fur Elektrotechnik)*, vol. 90, no. 6, pp. 443–453, 2007. [Online]. Available: http://dx.doi.org/10.1007/s00202-007-0095-x

- [19] H. Fathabadi, "Stability analysis of circuits including BJT differential pairs", *Microelectronics Journal*, no. 41. pp. 834–839, 2010. [Online]. Available: http://dx.doi.org/10.1016/j.mejo.2010.07.008

- [20] D. N. Loizos, P. P. Sotiriadis and G. Cauwenberghs, "A translinear SiGe BiCMOS current-controlled oscillator with 80 Hz–800 MHz tuning range", *Analog Integrated Circuits and Signal Processing*, vol. 52, no. 1-2, pp. 107–115, 2008. [Online]. Available: http://dx.doi.org/10.1007/s10470-008-9185-6

- [21] D. R. Frey, "Log-domain filtering: an approach to current-mode filtering", *IEE Proc. Circuits, Devices and Systems*, vol. 140, no. 6, pp. 406–416, 1993.

- [22] S. A. Tekin, H. Ercan and M. Alçı, "A new temperature compensated current controlled conveyor", *Informacije MIDEM Journal of Microelectronics, Electronic Components and Materials*, vol. 41, no. 1, pp. 22–26, 2011.

- [23] A. Fabre, M. Alami, "Universal current mode biquad implemented from two second generation current conveyors" *IEEE Transactions* on Circuits and Systems-I: Fundamental Theory and Applications, vol. 42, no. 7, pp. 383–385, 1995. [Online]. Available: http://dx.doi.org/10.1109/81.401151