ELECTRONICS AND ELECTRICAL ENGINEERING

ISSN 1392 - 1215 -

ELEKTRONIKA IR ELEKTROTECHNIKA

2009. No. 1(89)

ELECTRONICS

### ELEKTRONIKA

### Thin Film Transistors Gas Sensors: Materials, Manufacturing Technologies and Test Results

### M. C. Pereira, M. J. Martins, O. Bonnaud

T170

*Esc. Sec. de Gama Barros, Instituto Superior Técnico, Institut d'Electronic et Telecommunications de Rennes e-mail: mcpereira\_80@yahoo.com, mariajoaomartins@ist.utl.pt, olivier.bonnaud@univ-rennes1.fr*

#### Introduction

Five of the most important performance specifications of a sensor are its sensitivity, linearity, frequency response, long-term stability and power consumption. Sensor sensitivity and linearity are important characteristics for high accuracy and high precision Environment, measuring systems. health. telecommunications and the automobile industries are driving research and development of further integrated multi-function and adaptive systems that feed on multifrequency information provided by sensors with smaller power consumptions. And in some specific environment and health applications, long-term stability measurements is one the most important specifications.

Thin-film sensors are emerging as one of the most promising technologies for the manufacture of sensor blocks for those systems. These sensors are used in application-oriented systems, manufactured at smaller temperatures with reproductable and high-production techniques. Thin film sensors can also be integrated with post-signal processing CMOS technologies and consequently with low manufacturing and low maintenance cost systems.

In the next section, the authors analyse the evolution of large area electronics gas sensors and focus on the breakthroughs of thin-film transistors (TFTs) based technologies. The general characteristics of thin-film transistor (TFT) technologies are presented in the following sections: the structure of TFTs, the physical and electrical properties of the materials used in TFTs and how those properties are affected by the manufacturing processes parameters. A physics description and models overview of the thin film transistor (TFT) is discussed in the fifth section. The next section presents the structure, materials and manufacturing processes of air-gap thin-film transistors. Test and characterisation results are also discussed in this section. Air-gap thin-film transistors working as gas sensors present high sensitivity values in the presence of specific molecules, which could lead to new developments. Conclusions based on the five performance characteristics of a sensor, mentioned in the beginning of this introduction are presented in the last section of this paper.

# Large Area Electronics Gas Sensors: the State-of-the-Art

The development of large area electronics at low temperatures is playing an ever-increasing role in medical, environment and automobile industries. The research over the last two decades in this area, namely on gas sensors, has led to:

- Time responses within tens of seconds to a few seconds for most examples with organic thin films <sup>1-3</sup> and semiconductor tellurium films<sup>4</sup>, compared to a little more then a second for the tin oxide gas sensor <sup>5, 6</sup>, due to carrier mobility differences. Recovery times vary from a few minutes <sup>6</sup>, and tens of seconds for the PcPb films<sup>1</sup>, and a few seconds for air-gap thin-film transistors<sup>7</sup>.

- Sensitivity evolution within tens of vpm<sup>1-2</sup>, 0.7 ng/ppm<sup>3</sup> for organic thin film sensors, and 50 V for 500 ppm for the tellurium sensor<sup>4</sup> varying with the gas concentration and operation temperature. Air-gap thin-film transistors present a linear variation of the drain current with humidity concentration of  $10^6$  between 20% to 60% humidity ratios <sup>7</sup>. Linear behaviour was also observed for the tellurium sensor from 0-100 ppm<sup>4</sup>.

- Power consumption reduction from 1 W<sup>-1</sup> to tens of mW<sup>6</sup>, due to a reduction of size and mass of the heated membrane, thus allowing a pulse control of the temperature and reduction of switching times to milliseconds.

Several tests were also performed in deposition film methods, improving transistor stability and film conductivity. Thin-film transistor mobilities varied from tens of  $cm^2/V.s$  using a low pressure chemical vapour deposition method<sup>8</sup> to hundreds of  $cm^2/V.s$  with Metal Induced Lateral Crystallization (MILC)<sup>9</sup>.

Some research for the development of organic film transistors arrangements in arrays for selective gas recognition will lead to the development of the e-nose <sup>2</sup>. Another trend is the pursuit of sensors compatible and integrated with the VLSI/CMOS processes.

Several technological challenges still remain and TFT sensors present several advantages over other technologies namely:

- Higher sensitivity than capacitive sensors and that it could surpass top sensitivity values of some organic thin film sensors <sup>1-2</sup> and some metallic oxide sensors <sup>4-6</sup>, by using transistors instead of chemiresistors or other carrier mobility substrates <sup>1</sup>.

- Higher carrier mobility in thin films of polycrystalline silicon will yield lower sensor switching times than in organic thin film sensors<sup>9</sup>. The time of recovery is also influenced by the carrier mobility <sup>1-6</sup>, related also to the reversibility of the sensor (small hysteresis).

- Reproducibility at low cost and manufacture process compatibility with driven systems (silicon-on-insulator based process), allowing future integration of a hole signal processing system following the trend in gas sensors and bio sensors.

- Higher reliability, long-term stability and lower power than metallic oxide gas  $sensors^{5-6}$  due to the non-existence of heaters.

#### The Structure and Manufacture poly-Si TFTs

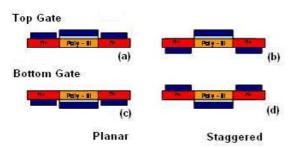

Fig. 1. Schematic diagrams of poly-Si TFTs: top-gate poly-Si TFT (a and b);down-gate poly-Si TFT (c and d)  $^8$

Unlike CMOS FETs, poly-Si TFTs are laid out on glass substrates at lower temperatures (smaller than 700°C) and are used for large area applications (in the order of a few microns). As represented in figure 1, a TFT can be structured with the gate above or below the semiconductor layer. The drain and source contacts can also be positioned on the same side or in opposite sides as the gate contact to the poly-Si film.

The manufacture of thin film transistors follows an adapted sequence of mask definition, layer deposition and layer etching processes as the manufacture of CMOS circuits. The substrate is covered with an insulator, usually silicon nitride or silicon oxide, that isolates the device from the alkaline and water impurities contained in the glass. For the top gate planar structure (figure 1.a), the poly-Si film is deposited first, followed by the gate insulator film (silicon oxide). A metal film (aluminium) is deposited next to define the island of the gate contact. Next, ionimplantation of doping impurities and doping activation defines the source and drain regions not protected by the gate contact metal film (in-situ doping process). Another method uses the deposition of a doped Si layer for amorphous silicon TFTs (as-Si TFTs) of LCD screens. A new insulator layer is deposited and holes for the source and drain contacts are etched. A metal deposited layer defines those contacts. A thick silicon nitride or silicon oxide protective layer is deposited for mechanical, chemical and electrical protection of the device.

The deposition parameters of the poly-Si film, such as the temperature and the pressure determine the atoms arrangement of the film. For some intervals of pressure and temperature, the final result is a poly-Si film in the crystalline state, while for others the film remains in the amorphous state. For this latter situation crystallization and post-treatment processes are needed.

## Materials and Process Parameters for the Manufacture of Poly-Si TFTs

For the manufacture of poly-Si thin film transistors (TFTs), two structural materials are mainly used: aluminium and polycrystalline silicon. Silicon oxide and silicon nitride are the insulator materials with the highest chemical compatibility with silicon, and therefore used as chemical, diffusion, thermal or mechanical barriers in the TFT structure.

The Polycrystalline Silicon Film. A high-quality polycrystalline silicon film is composed by grains or crystallites with longitudinal dimensions higher than the thickness of the film, without any internal defects and with small grain boundaries without any amorphous material. The generation of large grains in the film can be explained by the presence of few crystal seeds (low nucleation rate) that usually appear near the border between the base of the film and the insulator of the substrate. During crystallization, these seeds compete for amorphous material, rapidly growing in size. However, depending on the conditions of the crystallization process, this can lead to local areas of abrupt energy stabilization before all the amorphous material between the grains has been crystallized, forming a low quality film, with very small mobilities or even unusable TFTs. On the other hand, a high number of seeds (high nucleation rate) generate a large number of smaller grains without any or little internal defects and with very small borders. In these borders, the atoms of one grain usually connect directly to the atoms of the border grains. The bonds in the grain boundaries are weaker than the connections in the lattice. In silicon there are mainly tilted boundaries that have less structural disorder and smaller interfacial energies than the less common twisted boundaries <sup>10</sup>. The atoms arrangements are defined by their orientation in the <xyz> space axes and by  $\Sigma n$ , where n is the number of atoms involved in periodic arrangements at those boundaries.

The size, orientation, distribution and quality of crystallites of the poly-Si film influences the electrical parameters of the TFT, like the mobility of free carriers. And as mentioned before, all of these physical characteristics are related with the film deposition method and its parameters (pressure and temperature). Silicon direct deposition techniques for thin film substrates are LPCVD (Low Pressure Chemical Vapour Deposition), PECVD (Plasma Enhanced Chemical Vapour Deposition) and the sputtering of silicon.

In Low Pressure Chemical Vapour Deposition (LPCVD) the deposited material is generated by thermal decomposition (pyrolysis) of precursor gases like silane

(SiH<sub>4</sub>) or disilane (Si<sub>2</sub>H<sub>6</sub>) according to the chemical reactions: SiH<sub>4</sub> (g)  $\rightarrow$  Si (s) + 2H<sub>2</sub> (g) or Si<sub>2</sub>H<sub>6</sub> (g)  $\rightarrow$  2Si  $(s) + 3H_2$  (g), respectively. Part of the generated hydrogen is captured in the grain boundaries, depending on the temperature (and on the pressure in a smaller degree) of the deposition process. A hydrogenation step or plasma exposure diffuses out part of the hydrogen, decreasing the number of dangling bonds in the grain boundaries, thus decreasing the reverse mode currents and increasing the threshold voltage in modulus<sup>11</sup>. So a little hydrogen is in fact, beneficial by improving the TFT electrical characteristics, but its presence in the film contributes to thermal instability <sup>8</sup>. A fine tuning in the temperature during deposition will assure adequate hydrogen "infiltration". The deposited film has crystalline properties for temperatures over 550°C and pressures below 10<sup>-1</sup> Torr and is in the amorphous state at temperatures from 500°C to 550°C, and pressures near 90 Pa<sup>12</sup>. Best results have been obtained for the latter, after additional crystallization and post-treatment processes<sup>8</sup>.

In PECVD (Plasma Enhanced Chemical Vapour Deposition) the silicon film is generated through a chemical reaction by plasma at 200°C up to 450°C using precursor gases like silane  $(SiH_4)$  + fluoride  $(SiF_4)$  + hydrogen  $(H_2)$  or silane  $(SiH_4)$  + hydrogen  $(H_2)$  or silane  $(SiH_4)$  + dichlorosilane (DCS)  $(SiH_2Cl_2)$  + hydrogen  $(H_2)$ or other combinations of feed gases<sup>8, 13, 14</sup>. The substrate bias voltage controls the size of the crystallite. The size of the grain depends also on the substrate temperature, RF power and gas composition. The temperature controls the hydrogen content on the film like in the LPCVD process. For PECVD, better mobilities for top gate TFTs were obtained for 450 °C with  $SiH_4 + SiF_4 + H_2 - 44 \text{ cm}^2/\text{V.s}$  and for 230°C with SiH<sub>4</sub> + SiH<sub>2</sub>Cl<sub>2</sub> + H<sub>2</sub> - 20 cm<sup>2</sup>/V.s  $^{8, 14}$ . As a comparison with the previous deposition method, for LPCVD at 550° C and 100 Pa, it was measured a mobility of 53 cm<sup>2</sup>/V.s <sup>8</sup>. Note that in this last TFT, the Silicon film was deposited in the amorphous state.

The other deposition method is sputtering, a physical process whereby atoms from a target material (doped or undoped) are ejected as a gas, due to bombardment by energetic ions or plasma, and deposited towards the substrate. The plasma may contain neutral species like SiH<sub>2</sub> and SiH<sub>3</sub>, and other ionic species SiH<sub>x</sub> with x varying from 0 to 4. The deposited material is in the amorphous state with grain sizes smaller than 10 nm <sup>8</sup>.

If the film is deposited in the amorphous state, a crystallization step is needed. There are two main techniques:

1. Solid Phase Crystallization (SPC), that for best mobility results is used in a two-phase process: crystallization at low temperature ( $600^{\circ}$ C) for a low nucleation rate that will lead to the formation of large grains and a high temperature annealing ( $900^{\circ}$ C) to improve the grain quality by diffusing out the hydrogen content.

2. Laser crystallization used to obtain large grains by delaying the cooling process. The electrical field mobility reached  $350 \text{ cm}^2/\text{Vs}$  with a standard deviation of 5%<sup>15</sup>.

**The Aluminium Film.** Aluminium is used as structural material in MEMS in spite of its smaller mechanical resistance to stress than polysilicon. A 150 nm

thick film of polysilicon outstands up to 400 MPa of stress <sup>16</sup>. The deposition of aluminium is made in an air-tight chamber where a piece of solid aluminium with over 99,9% of purity is fused by Joule effect on a resistance. When the aluminium is in the liquid phase, the air is extracted from the chamber to create a vacuum that pulverizes homogenously the substrates attached to the top of the chamber. The film thickness is measured by spectrometry in nanometres.

#### **Dielectric Materials.**

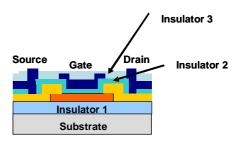

**Fig. 2.** Insulators for poly-Si TFT<sup>8</sup>

In the manufacture of thin film transistors, dielectric materials can have one or more functions according to the position in the TFT structure. Insulator one, the dielectric above the substrate is a <u>thermal barrier</u> during crystallization and a <u>diffusion barrier</u> to prevent contamination namely from water ions and alkaline ions of the glass substrate. Silicon nitride  $(Si_3N_4)$  films are better diffusion barriers than silicon oxide films.

The main requirement of the gate insulator is its electrical stability. The gate insulator influences several TFT electrical parameters, namely:

- The threshold voltage  $(V_T)$  that depends on the presence of charges in the insulator. This effect can be compensated by a higher doping level;

- The subthreshold slope (S) that depends on the fixed charges in the semiconductor and on the density of interface defects<sup>8</sup>;

- The field effect mobility ( $\mu_{FET}$ ) that degrades due to the scattering of electrons caused by defects at the insulator-semiconductor interface. To lower the defect density at the gate insulator-semiconductor interface, the choice of a dielectric goes to the best chemically compatible material: silicon dioxide (SiO<sub>2</sub>). Silicon nitride is a poor interface for poly-Si. To take advantage of its higher mechanical resistance a silicon nitride with silicon oxide dual gate TFT has been experimented in a TFT that showed a better  $I_D(V_G)$  characteristic than an APCVD SiO<sub>2</sub> gate insulator regular TFT  $^{17}$ .

The dielectric above the device protects it from mechanical, chemical and electrical damages. A thick layer of silicon oxide is normally used.

The tetrahedral arrangements of silicon to oxygen atoms are formed by thermal oxidation of poly-Si or by the deposition of silicon oxide on silicon or glass substrates at low temperatures. The deposition of silicon oxide can be done by Physical Vapour Deposition (PVD) using RF sputtering or by Chemical Vapour Deposition (CVD) using LPCVD or PECVD. Silicon Nitride can be deposited by LPCVD for glass substrates or by PECVD. The latter method is mainly used for the deposition of silicon nitride as gate insulator of hydrogenated as-Si TFTs.

#### Physics and Modelling of the poly-Si TFT

**Physics Behaviour.** The poly-crystalline structure of the TFT can be roughly described by internal defect free crystallites and their boundaries. The defect free crystallites have similar properties to those of monocrystalline silicon of VLSI FETs. The energy band diagram has a minimum conduction energy level and a maximum valence energy level with a gap of 1.12 eV (crystalline silicon), with no energy states between them.

Grain boundaries can be modelled as amorphous silicon. The difference between the minimum energy level of the conduction band and the maximum energy level of the valence band is 1.71 eV. Between those levels, there are several energy states with higher density of donor states near the valence level, and with higher density of acceptor states near the conduction level. These states are created due to distortions in the atomic bonds, unfilled or pending bonds with amphoteric behaviour and mainly due to the precipitation of doping atoms at the boundaries. The hydrogenation post-treatment passivates the dangling bonds, reducing the density of boundary states.

The difference in energy levels from crystallites to grain boundaries forms bends in the energy bands that behave as potential barriers from a crystallite to its neighbours. Assuming a columnar grain structure and a solid phase crystallization (SPC) method, these potential barriers are transversal to the current flow. For a n-type TFT, the grain boundary potential barriers decrease with increasing gate voltage and with increasing drain voltage (drain induced grain barrier lowering). The increase of the gate voltage frees carriers from the poly-Si to the channel region. In the thin film transistor, the drain current curve with the gate voltage changes from an exponential regime to a linear regime, as the gate voltage reaches the threshold value. The threshold voltage in TFT has a different meaning than the one used for MOSFET. The formation of the channel voltage is named "turn-on" voltage for the poly-Si n-type TFT. The threshold voltage is the gate voltage at which the relation  $I_D(V_{GS})$  stops being exponential. The difference between these two values is typically 1 V<sup>18</sup>. The gate to source voltage and the drain to source voltage define the regions of operation of the TFT. Each region of operation is also characterized by a drain to source current resulting from the contribution of several conduction mechanisms.

**Conduction Mechanisms.** The conduction mechanisms in the crystallites are those of the MOSFET: drift of carriers mainly above the threshold region, and diffusion of carriers mainly at the subthreshold region. At the grain boundaries, in the conduction mode, there are two mechanisms<sup>11</sup>:

1. The carriers tunnel-through the grain boundary between the crystallites, when the extension of the space charge region is much smaller than the width of the crystallite, considering a cubic shape for all grains among other assumptions defined by the Seto's model<sup>8</sup>. The extension of the space charge region can be further minimized with higher doping concentrations.

2. When the extension of the space charge region is larger than the critical value defined by the Seto's model (the width of the crystallite), related with a higher height of the energy barrier, thermoionic emission causes electron scattering in the grain boundaries. The total scattering is given by:

$$\frac{1}{\mu} = \frac{1}{\mu_G} + \frac{1}{\mu_{eff}} \,. \tag{1}$$

In equation (1) the mobility in the film ( $\mu$ ) is related to the scattering in the grain ( $\mu_G$ ) and the scattering at the boundaries ( $\mu_{eff}$ ) in an analogy with two resistances in series. In the saturation, the mobility of free carriers is characterised by  $\mu_G$  that decreases with the temperature. Before saturation,  $\mu_{eff}$  is the main factor and it increases with the temperature. At low temperatures or with high trap concentration, or at low voltage  $\mu_{eff}$  is the main scattering factor.

In the reverse mode, a reverse bias causes an electric field that occurs mainly at the grain boundaries. At the grain boundaries there are three possible conduction mechanisms:

1. The generation of free carriers on both sides of the grain boundary at the depletion region that is usually much wider than the grain boundary itself.

2. Trap-to-trap tunnelling at grain boundaries, that occurs when the density of traps is high especially at lower temperatures;

3. Fowler-Nordheim effect at the grain boundary or conduction generated by field enhanced thermal generation observed in poly-Si diodes.

**Brief Notes on Models for poly-Si TFT.** There are mainly three types of models: models based on the physics related to individual grain boundaries <sup>19</sup>, models supported on current-voltage characteristics <sup>20</sup> and models built on empirical approaches to manufactured and tested devices <sup>21</sup>.

Some models started with expressions for poly-Si characteristics like the height of the energy barrier at the grain boundaries and later incorporated in current-voltage equations. Several empirical results based on long-channel devices (above 6 µm) were added for accurate simulation values. Later versions include short-channel effects (like the Kink effect), the field-effect mobility in moderate inversion, and subthreshold currents. Most recent models for TFTs based on empirical measurements include equations for the reverse-bias leakage current of the drain junction and the subthreshold leakage current<sup>22</sup>, drain induced barrier lowering, temperature effects<sup>23</sup> and mobility degradation at high voltage bias. To ensure SPICE convergence, most models use the same set of equations to describe all regimes (subthreshold, above threshold, saturation and kink regimes)<sup>24</sup>. For the drain current, the unified model can be obtained by:

$$\frac{1}{I_d} = \frac{1}{I_{sub}} + \frac{1}{I_a}.$$

(2)

In equation (2), the drain current is the combination of currents in the sub threshold and above threshold regions. As mentioned before, the drift of carriers occurs mainly above the threshold region, and diffusion of carriers occurs mainly at the subthreshold region.

#### **Air-Gap Thin Film Transistors (AGTFTs)**

Manufacture of AGTFTs. Air-gap thin film transistors (AGTFT) or suspended gate thin film transistors<sup>7</sup>, are thin film transistors with a gaseous gate dielectric. A glass substrate covered with an insulator film of Silicon Nitride (Si<sub>3</sub>N<sub>4</sub>) is used to deposit by LPCVD, a 350 nm poly-Si film. The film is then crystallized by SPC at 600° C for 12 hours. The gate insulator film is then deposited and etched for the definition of the active area. In some transistors a thin protective layer silicon nitride is deposited, in others the choice for protective material goes to silicon oxide and the rest of the transistors were fabricated without any protective film over the active area. A temporary support film is then deposited, before the aluminium structural film, which will define the gate and the contacts for the drain and the source. The excess material is removed by etching agents.

**Characterization of AGTFTs.** The air-gap thin film transistor is characterized by the analysis of its regions of operation, the  $I_{ds} = f(V_{gs})$  transfer characteristic, the  $I_{ds} = f(V_{ds})$  output characteristic, and the values of four standard parameters used to compare these types of transistors with thin film transistors with a silicon oxide insulator. These parameters are:

- Threshold voltage (V<sub>T</sub>);

- Carrier mobility (µ);

- Voltage slope (S);

- $I_{\text{ON}} / I_{\text{OFF}}$  ratio.

The operation regions for the air-gap thin film transistor are analogous to the operation regions of the field effect transistor. The basic working principle of the air-gap thin film transistor is not different from other field effect transistors, in spite of the different dielectric material. The threshold voltage is related to the charge density in the channel and with the interface channeldielectric on the forbidden energy states and the capacitance between the gate and the channel per surface unit. The mobility depends on the TFT dimensions and also on the capacitance between the gate and the channel per surface unit.

**Test Results for the AGTFTs.** Three types of airgap thin film transistors were studied in environment controlled conditions. The first type has no protection on the active area, while the other two have the channel protected by a layer of 50 nm of silicon oxide or by a layer of 15 nm of silicon nitride, respectively. Some of the results can be summarized in the following statements:

There was a degradation of the characterization parameters of the air-gap thin film transistor for neutral gases (such as nitrogen and oxygen). For those gases the threshold voltage and the voltage slope increased.

There was an improvement of the characterization parameters of the air-gap thin film transistor for increasing levels of humidity. The AGTFT presented a linear variation of the drain current with the humidity concentration of  $10^6$  between 20% of humidity ratio and 60% humidity ratio.

The transistors with protected active area presented smaller sensitivity, but higher precision. The return time of the air-gap thin film transistor is in the order of seconds, increasing with the temperature.

#### Conclusions

The main development vectors in large area electronics for gas sensors were presented by focusing on thin-film transistor sensors. The structure, materials and manufacturing methods and parameters, and how they influence the electrical parameters of the transistor and in turn the sensor specifications were analysed. Thin-film transistor breakthroughs reported mainly in sensitivity, linearity and dynamic response promise new fields of applications for the sensors developed with these technologies. There are also some challenges on the power consumption and stability specifications that needed to be addressed. Some questions on sensors based on air-gap thin-film transistors are still unanswered and hamper the effort to design a commercial usable device.

#### References

- Guillaud G., Simon J., Germain J. P. Metallophthalocyanines gas sensors, resistors and field effect transistors // Coordination Chemistry Reviews. – 1998. – Vol. 178–180. – P. 1433–1484.

- Petty M. C. Gas sensing using thin organic films // Biosensors & Bioelectronics. – 1995. – Vol. 10. – P. 129– 134.

- Luisa Torsi, Cristina Tanese M., Nicola Cioffi, Maria. C. Gallazzi, Luigia Sabbatini, P. Giorgio Zambonin. Alkoxysubstituted polyterthiophene thin-film-transistors as alcohol sensors // Sensors and Actuators. – 2004. – Vol. B 98. – P. 204–207.

- Shashwati Sen, Muthe K. P., Niraj Joshi, Gadkari S. C., Gupta S. K. Jagannath, Roy M., Deshpande S. K., Yakhmi J. V. Room temperature operating ammonia sensor based on tellurium thin films // Sensors and Actuators. – 2004. – Vol. B 98. – P. 154–159.

- Jyh-Jier Ho, Fang Y. K., Wu K. H., Hsieh W. T., Chen C. H., Chen G. S., Ju M. S., Jing-Jenn Lin, Hwang S. B. High sensitivity ethanol gas sensor integrated with a solid-state heater and thermal isolation improvement structure for legal drink-drive limit detecting // Sensors and Actuators. – 1998. Vol. B 50. – P. 227–233.

- Jaegle M., Wollenstein J., Meisinger T., Bottner H., Muller G., Becker T., Bosch-v.Braunmuhl C., Micromachined thin film SnO<sub>2</sub> gas sensors in temperaturepulsed operation mode // Sensors and Actuators. 1999. – Vol. B 57. – P. 130–134.

- Mahfoz-Kotb H., Salaün A. C., Mohammed-Brahim T., and Olivier Bonnaud. Air-Gap Polycrystalline Silicon Thin-Film Transistors for Fully Integrated Sensors // IEEE Electron Devices Letters. – March 2003. – Vol. 24, No.3.

- 8. Yue Kuo, et al. In "Thin Film Transistors, Materials and Processes" Volume 2: Polycrystalline silicon thin film transistors. Kluwer Academic Publishers.

- Wang H., Chan M., Jagar S., Poon V. M. C., Qin M., Wang Y., and Ko P. K. Super thin-film transistor with SOI CMOS performance formed by a novel grain enhancement method // IEEE Trans. On Electron Devices. – 2000. – Vol. 47. – P. 1580.

- Kohyama M., and Yamamoto R. Theoretical Study of the Atomic and Electronic Structures of Grain Boundaries in Semiconductors // Polycrystalline Semiconductors III, Solid State Phenomena. – Switzerland: Scitec Publications, 1994. – Vol. 37–38. – P. 55–66.

- Tala-Ighil, Rahal A., Toutah H., Mohammed-Brahim T., Mourgues K., and Bonnaud O. Leakage Current of Unhydrogenated Solid Phase Crystallized Silicon TFT's // Polycrystalline Semiconductors V-Bulk Materials, Thin Films and Devices Eds. Werner J. H., Strunk H. P., Schock H. W. – Scitec Publications. – 1999. – Vol. 67–68. – P. 541.

- Guillet D., Sarret M., Lhermite H., Bonnaud O. Effect of pressure and temperature on the electrical properties of LPCVD silicon-germanium thin films Polycrystalline Semiconductor VI // Solid State Phenomena. – 2001. – Vol. 80–81. – P. 89–94.

- Woo J. L, Lim H. J., and Jin Jang. Polycrystalline silicon thin film transistors deposited at low substrate temperature by remote plasma chemical vapour deposition using SiF<sub>4</sub>/H<sub>2</sub> // Applied Physics Letters. – 1994. – Vol. 65. – P. 1644.

- 14. Mulato M., Chen Y., Wagner S., and Zanatta A. R. Microcrystalline silicon with high electron field-effect mobility deposited at 230°C // Non. Crys. Solids. – 2000. – Vol. 266 – P. 1260.

- 15. Helen Y., Dassow R., Nerding M., Mourgues K., Raoult F., Kölher J. R., Mohammed-Brahim T., Rogel R., Bonnaud O., Werner J. H., Strunk H. P. High mobility thin film transistors by Nd : YVO4 Laser crystallization // Thin Solid Films. 2001. Vol. 383. P. 143–146.

- Temple-Boyer P., Imbernon E., Rousset B., Sheid E. Residual stress of silicon films deposited by LPCVD from silane // Mat. Res. Soc. Symp. Proc. – 1998. – Vol. 518. – P. 209.

- Pichon L., Raoult F., and Bonnaud O. Comparison of the low-temperature (<600°C) polysilicon thin-film transistors with two kinds of gate dielectrics // Mat. Chem Phys. – 1995. – Vol. 39. – P. 313.

- Jacunski M., Shur M. S., and Hack M. Threshold voltage, field-effect mobility, and gate-to-channel capacitance in polysilicon TFT's // IEEE Trans. On Electron Devices. – 1996. – Vol. 43. – P. 1433.

- Lin P.-S., Guo J.-Y., and Wu C.-Y. A Quasi-Two Dimensional Analytical Model for the Turn-On Characteristics of Polysilicon Thin-Film Transistors // IEEE Trans. On Electron Devices. – 1990. – Vol. 37(3). – P. 666– 674.

- Chern H., Lee C., and Lei T. An analytical model for the above threshold characteristics of polysilicon thin-film transistors // IEEE Trans. On Electron Devices. – 1995. – Vol. 42. – P. 1240.

- 21. Shur M., Hack M., and Byun Y. Circuit model and parameter extraction technique for polysilicon thin-film transistors // Proc. ISDRS. 1993. P. 165.

- Adan H. Tsutsui and M. Morita. Analysis and model of leakage current mechanism in polysilicon MOS thin-film transistors // Proceedings Of ISDRS. – 1991. – P. 525.

- 23. Bhattacharya S., Banerjee S., Nguyen B., and Tobin P. Temperature dependence of the anomalous leakage current in polysilicon-on-insulator MOSFET's // IEEE Trans. On Electron Devices. – 1994. – Vol. 41. – P. 221.

- 24. **Iňiguez B., Xu Z., Fjeldly T. A., and Shur M.** Unified Model for Short-Channel Poly-Si TFTs // Solid State Electronics. 1999. Vol. 43. P. 1821–1831.

Received 2008 10 10

### M. C. Pereira, M. J. Martins, O. Bonnaud. Thin Film Transistors Gas Sensors: Materials, Manufacturing Technologies and Test Results // Electronics and Electrical Engineering. – Kaunas: Technologija, 2009. – No. 1(89). – P. 39–44.

The development of large area electronics gas sensors is reported, by focusing on the breakthroughs of thin-film transistor technologies. Thin-film transistors are analysed in terms of structure, their manufacturing materials and their properties. Deposition, crystallization and post-treatment methods and how the parameters of those methods affect the electrical properties of the thin-film transistor and in turn, the performance of the thin-film sensor, are also reported. A brief analysis on the structure, manufacture and test results of air-gap thin-film transistors, that showed high sensitivity values for certain gases, concludes this paper. Ill. 2, bibl. 24 (in English; summaries in English, Russian and Lithuanian).

### М. С. Перейра, М. Е. Мартинс, О. Бонауд. Датчики газа на основе тонких пленок: материалы, технологии изготовления и результаты испытаний // Электроника и электротехника. – Каунас: Технология, 2009. – № 1(89). – С. 39–44.

Показано развитие крупноразмерных электронных датчиков газа. Большое внимание уделяется новейшим достижениям технологий транзисторов на основе тонких пленок. Транзисторы на основе тонких пленок анализируются с точки зрения их структуры, производственных материалов и их свойств. Анализируются: смещение, кристаллизация и методы постобработки, а также как особенности тех методов определяют электрические свойства транзисторов на основе тонких пленок. От этих особенностей зависят показатели датчиков указанного типа. Прведены: короткий анализ структуры, особенности изготовления и результаты испытаний транзисторов с воздушным диэлектриком. Результаты показали высокую чувствительность указанных датчиков к газам некоторых типов. Ил. 2, библ. 24 (на английском языке; рефераты на английском, русском и литовском яз.).

## M. C. Pereira, M. J. Martins, O. Bonnaud. Plonų plėvelių tranzistoriniai dujų jutikliai: medžiagos, gamybos technologijos ir bandymų rezultatai // Elektronika ir elektrotechnika. – Kaunas: Technologija, 2009. – Nr. 1(89). – P. 39–44.

Pristatomas didelio ploto elektroninių dujų jutiklių projektavimas. Daugiau dėmesio skiriama plonų plėvelių tranzistorių technologijoms. Analizuojama plonų plėvelių tranzistorių struktūra, gamybos metu naudojamos medžiagos ir jų savybės. Taip pat apžvelgiami nusodinimo, kristalizavimo ir pogamybinio apdorojimo metodai, taip pat šių metodų parametrai lemia elektrines plonų plėvelių tranzistorių savybės. Nuo šių savybių priklauso plonos plėvelės jutiklio efektyvumas. Trumpai analizuojama plonų plėvelių tranzistorių su dujiniu dielektriku struktūra, gamyba ir bandymų rezultatai. Parodyta, jog tokie tranzistoriai yra ypač jautrūs tam tikrų rūšių dujoms. Il. 2, bibl. 24 (anglų kalba; santraukos anglų, rusų ir lietuvių k.).